# Entwicklung eines Echtzeit-Strahlprofil-Monitoring-Systems für das COMPASS-II Experiment

Christoph Michalski

Fakultät für Mathematik und Physik Albert-Ludwigs-Universität Freiburg

# Entwicklung eines Echtzeit-Strahlprofil-Monitoring-Systems für das COMPASS-II Experiment

## Diplomarbeit

vorgelegt von

Christoph Michalski

Physikalisches Institut Albert-Ludwigs-Universität Freiburg

März 2013

# Inhaltsverzeichnis

| 1 | Ein | leitung                                                           | 1  |

|---|-----|-------------------------------------------------------------------|----|

| 2 | Phy | sikalische Grundlagen                                             | 5  |

|   | 2.1 | Der Spin des Nukleons                                             | 6  |

|   | 2.2 | Tief-inelastische Lepton-Nukleon-Streuung                         | 7  |

|   | 2.3 | Die Parton-Verteilungsfunktionen                                  | 8  |

|   |     | 2.3.1 Unpolarisierte Parton-Verteilungsfunktionen                 | 9  |

|   |     | 2.3.2 Die longitudinal polarisierten Parton-Verteilungsfunktionen | 9  |

|   | 2.4 | Generalisierte Parton-Verteilungen                                | 10 |

|   |     | 2.4.1 Kinematische Variablen                                      | 10 |

|   |     | 2.4.2 Zusammenhang der GPDs mit bekannten Verteilungen            | 12 |

|   |     | 2.4.3 Stoßparameterabhängige Parton-Verteilungen                  | 13 |

|   | 2.5 | Tief-virtuelle Compton-Streuung                                   | 14 |

| 3 | Das | COMPASS-II Experiment                                             | 17 |

|   | 3.1 | Der Strahl                                                        | 18 |

|   | 3.2 | Das Flüssigwasserstoff-Target                                     | 19 |

|   | 3.3 | Das COMPASS-II-Spektrometer                                       | 20 |

|   |     | 3.3.1 Spurdetektoren                                              | 23 |

|   |     | 3.3.2 Der CAMERA-Detektor                                         | 24 |

|   | 3.4 | Das COMPASS-II-Trigger-System                                     | 26 |

|   |     | 3.4.1 Der Myontrigger                                             | 26 |

|   |     | 3.4.2 Der Protontrigger                                           | 27 |

|   | 3.5 | Die Datennahme                                                    | 29 |

| 4 | Das | GANDALF Framework                                                 | 31 |

| _ | 4.1 | Das GANDALF Mainboard                                             | 32 |

|   | 4.2 | Schnittstellen des GANDALF-Moduls                                 | 33 |

|   |     | 4.2.1 VME64x                                                      | 33 |

|   |     | 4.2.2 VXS                                                         |    |

|   |     | 4.2.3 Takt- & Trigger-Schnittstelle                               | 34 |

|   | 4.3 | Taktsignale                                                       | 35 |

|   | 4.4 | Aufsteckkarten                                                    | 36 |

|   |     | 4.4.1 Die Gimli-Karte                                             | 36 |

|   |     | 4.4.2 Die digitale Mezzanine-Card                                 | 36 |

|   | 4.5 | Das TCS Interface                                                 | 37 |

|   | 4.6 | Das CPLD Interface                                                | 38 |

|   | 4.7 | Field Programmable Gate Array                                     | 40 |

iv Inhaltsverzeichnis

|              |     | 4.7.1<br>4.7.2 | Allgemeines zu FPGA                            |       |

|--------------|-----|----------------|------------------------------------------------|-------|

| 5            | Ent |                | ng eines Zählers mit totzeitfreier Auslese     | 45    |

| J            | 5.1 |                | p eines Scalers                                |       |

|              | 5.2 |                | iedene Codes und deren Vor- und Nachteile      |       |

|              | 0.2 | 5.2.1          | Binär- und Gray-Code                           |       |

|              |     | 5.2.1 $5.2.2$  | One-Hot- und Johnson-Code                      |       |

|              | 5.3 | _              | caler-Design                                   |       |

|              | 0.0 | 5.3.1          | Vorgaben                                       |       |

|              |     | 5.3.2          | Johnson-Ringzähler und Johnson-Register        |       |

|              |     | 5.3.3          | Dekoder und Triggerverzögerung                 |       |

|              |     | 5.3.4          | Subtraktion, Addition und Gate-Funktion        |       |

|              |     | 5.3.5          | Zusammenfassung des 1-Kanal-Scaler-Designs     |       |

|              |     | 5.3.6          | Implementierung des 1-Kanal-Scaler-Designs     |       |

|              |     | 5.3.7          | Multiplexer und Zwischenspeicherung            |       |

|              |     | 5.3.8          | Ressourcenverbrauch                            |       |

|              |     |                |                                                |       |

| 6            |     |                | ng von Scaler und TDC auf einem GANDALF-Modul  | 61    |

|              | 6.1 |                | ınktionsweise des TDC                          |       |

|              | 6.2 |                | seudo-Randomtrigger                            |       |

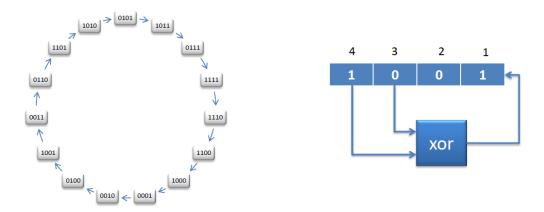

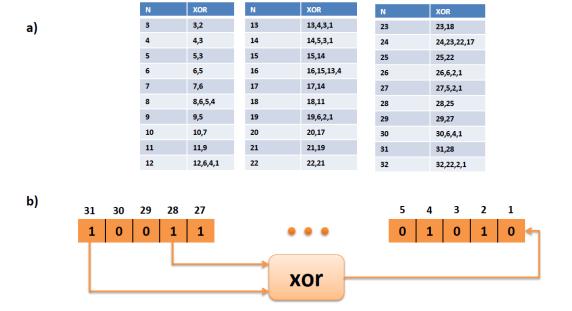

|              |     | 6.2.1          | Linear rückgekoppelte Schieberegister          |       |

|              |     | 6.2.2          | Erzeugung einer künstlichen Spillstruktur      |       |

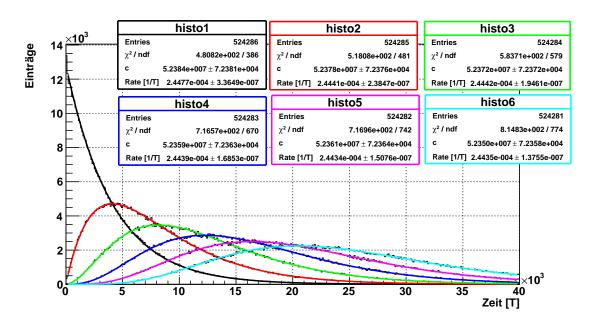

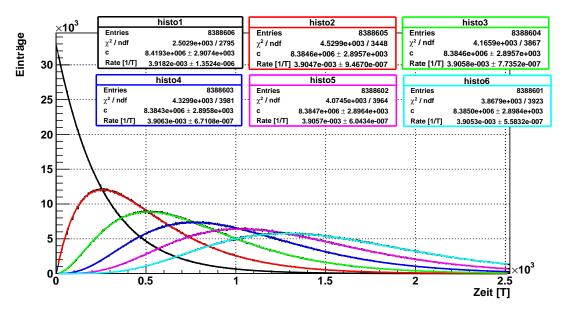

|              |     | 6.2.3          | Test auf zeitliche Zufälligkeit des Signals    |       |

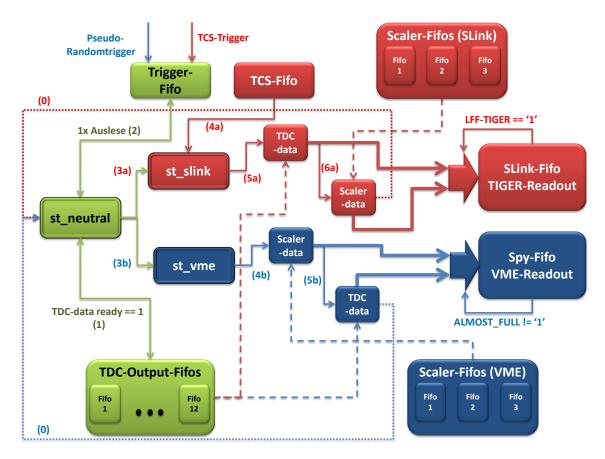

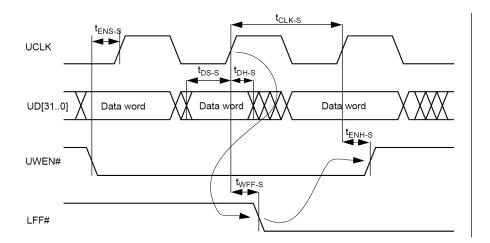

|              | 6.3 | Die Da         | atenauslese                                    | . 71  |

| 7            | Ver | ifikatio       | on und Einbindung in das COMPASS-II Experiment | 75    |

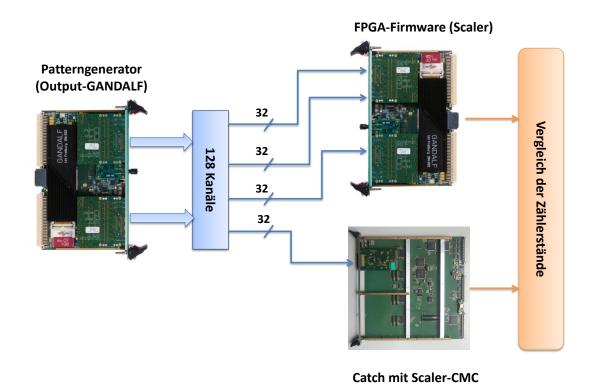

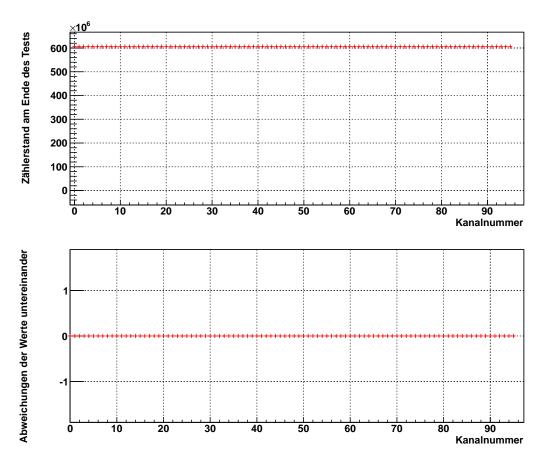

|              | 7.1 |                | messungen                                      |       |

|              | 7.2 |                | dung in das COMPASS-II Experiment              |       |

|              |     | 7.2.1          | FI02                                           |       |

|              |     | 7.2.2          | Das Monitoring-System                          | . 83  |

|              | 7.3 | _              | nisse der Messungen am COMPASS-II Experiment   |       |

|              |     | 7.3.1          | Scaler-Daten                                   |       |

|              |     | 7.3.2          | TDC-Daten                                      | . 92  |

| 8            | Zus | ammei          | nfassung                                       | 101   |

| $\mathbf{A}$ | Dat | enforn         | nat der Pseudo-Random-Daten                    | 103   |

| В            | Dat | enforn         | nat der TCS-Daten                              | 107   |

|              |     |                |                                                |       |

| $\mathbf{C}$ |     |                | Parameter für die TDC-Scaler-Firmware          | 109   |

|              |     |                | und Scaler-Hex-ID                              |       |

|              | C.2 |                |                                                |       |

|              | C.3 | Scaler         | und Pseudo-Randomtrigger                       | . 109 |

| D            | VH  | DL-Cո          | de Beispiele                                   | 111   |

|              |     |                | al Scaler-Design                               |       |

|              |     |                | onenten                                        |       |

| Inhaltsverzeichnis | V |

|--------------------|---|

|                    |   |

|         | D.2.1  | Johnson-Counter | <br>1 | 14 |

|---------|--------|-----------------|-------|----|

|         | D.2.2  | Dekoder         | <br>1 | 15 |

|         | D.2.3  | Subtrahierer    | <br>1 | 15 |

|         | D.2.4  | Addierer        | <br>1 | 16 |

|         | D.2.5  | 31 Bit-Register | <br>1 | 17 |

| D.3     | Pseudo | o-Randomtrigger | <br>1 | 17 |

|         |        |                 |       |    |

| Literat | urverz | eichnis         | 1     | 21 |

# 1. Einleitung

Seit Menschengedenken findet die Suche nach den kleinsten Bausteinen der Materie statt. Schon am Ende des 19. Jahrhundert konnte gezeigt werden, dass Atome nicht unteilbar sind, was neue Fragen nach den kleinsten Materiebausteinen aufwarf. Wesentlich dazu beigetragen haben Experimente von E. Goldstein und J. Thomson. Goldstein gelang es 1886, Atomen Elektronen zu entreißen, womit auf die Existenz von geladenen Teilchen innerhalb nach außen hin neutraler Atome geschlossen werden konnte [1]. Etwa zehn Jahre später konnte Thomson die negativ geladenen Elektronen mit der Kathodenstrahlröhre nachweisen [2]. Zum damaligen Zeitpunkt herrschte jedoch noch Unklarheit über die Massenverteilung innerhalb der Atome. Im Jahr 1911 konnte E. Rutherford durch Streuversuche mit Helium-Kernen an dünnen Goldfolien die damals vorherrschende Vermutung widerlegen, die Bestandteile der Atome seien "wie Rosinen in einem Kuchenteig" verteilt. Diese besitzen einen massiven Kern, umgeben von einer fast masselosen Hülle, der Elektronenhülle [3].

Heute wissen wir, dass die sichtbare Materie des Universums größtenteils aus Elektronen und Nukleonen<sup>1</sup> besteht. Elektronen  $e^{\pm}$  sind Elementarteilchen und gehören der Gruppe der Leptonen an. Weitere Vertreter sind Myonen  $\mu^{\pm}$  und Tauonen  $\tau^{\pm}$ , die sich von den Elektronen nur durch ihre Massen unterscheiden. Sie wechselwirken elektromagnetisch und schwach. Zusammen mit den schwach wechselwirkenden Neutrinos  $\nu_e$ ,  $\nu_{\mu}$ ,  $\nu_{\tau}$  beziehungsweise deren Antiteilchen werden die Leptonen in drei Generationen,  $(1, \nu_l)$  mit  $1 = \{e, \mu, \tau\}$ , zusammengefasst.

Im Gegensatz dazu gehören Nukleonen zur Gruppe der Hadronen, welche einen Zusammenschluss von mehreren Elementarteilchen darstellen, die der starken Wechselwirkung unterworfen sind. Diese lassen sich in zwei Untergruppen, Mesonen und Baryonen, unterteilen. Während Mesonen aus einem Quark-Antiquark-Paar aufgebaut sind und ganzzahligen Spin tragen, bestehen Baryonen aus drei Quarks. Die Addition der einzelnen Quark-Spins resultiert im Falle der Baryonen in einen halbzahligen Spin.

<sup>&</sup>lt;sup>1</sup>Nukleonen bezeichnen die massiven Bausteine des Atomkerns, also Protonen und Neutronen.

2 1. Einleitung

Messungen des anomalen magnetischen Moments des Nukleons [4, 5], waren erste Hinweise auf eine Substruktur desselben. Heute ist bekannt, dass neben dem Nukleon noch viele andere Hadronen existieren. Diese Erkenntnis hat man vor allem Experimenten mit Teilchenbeschleunigern und Messungen der Höhenstrahlung zu verdanken [6]. Die Beschreibung der Wechselwirkungen zwischen bekannten Elementarteilchen und deren Einordnung in Teilchenfamilien ist unter dem Begriff "Standardmodell" bekannt.

Unabhängig voneinander postulierten George Zweig und Murray Gell-Mann 1964, dass Hadronen ihrerseits aus noch kleineren Teilchen bestehen, welche "Quarks" genannt wurden [7, 8]. Dadurch war eine Schematisierung des hadronischen "Teilchenzoos" möglich, ähnlich der Einordnung chemischer Elemente in das Periodensystem. Ende der 1960er Jahre erfolgten erstmals Messungen zur Untersuchung von Nukleonen mittels tief-inelastischer Elektron-Nukleon-Streuung, womit die Existenz punktförmiger Teilchen innerhalb von Hadronen bestätigt werden konnte. Diese Teilchen wurden Partonen genannt.

Heute ist bekannt, dass das Nukleon aus drei "Valenzquarks" und mehreren Gluonen und Seequarks aufgebaut ist. Gluonen sind im Gegensatz zu Quarks elektrisch neutral. Sie bilden die Austauschteilchen der starken Wechselwirkung und koppeln an alle Teilchen die sogenannte Farbladung tragen. Dazu gehören sowohl Quarks als auch Gluonen selbst [9]. Valenzquarks bestimmen die Quantenzahlen des Hadrons, wie beispielsweise die elektrische Ladung oder die Parität. Seequarks sind virtuelle Quark-Antiquark-Paare die durch Gluonen gebildet werden. Durch ihre Erzeugung und Vernichtung kommt es innerhalb des Hadrons zu Vakuumfluktuationen. Diese Paare bilden einen "See" um das Valenzquark in dessen unmittelbarer Umgebung der erwähnte Prozess stattfindet. Zwar tragen Seequarks nicht zu den Quantenzahlen des Hadrons bei, jedoch liefern sie einen Beitrag zu dessen Spin.

Mit dem EMC<sup>2</sup>-Experiment am CERN<sup>3</sup> konnte Ende der 1980 er Jahre widerlegt werden, dass sich der Nukleonspin nur aus den Spinbeiträgen seiner Quarks und Antiquarks zusammensetzt, da deren Spinbeiträge zu gering sind [10, 11]. Dies wurde als sogenannte "Spinkrise" bekannt. Auch der Spinbeitrag der Gluonen reicht nicht aus, um das "Spinpuzzle" zu lösen, was präzise Messungen der Gluonpolarisation am COMPASS<sup>4</sup>-Spektrometer ergaben. Bis heute ist die genaue Zusammensetzung der Spinstruktur des Nukleons noch unverstanden.

Eine Lösung des Spinpuzzles könnte das Konzept der Parametrisierung der hadronischen Wechselwirkung durch generalisierte Parton-Verteilungsfunktionen darstellen. Generalisierte Parton-Verteilungsfunktionen können über exklusive Prozesse, beispielsweise der tief-virtuellen Compton-Streuung (DVCS<sup>5</sup>), vermessen werden. Damit könnte eine Bestimmung totaler Drehimpulse von Quarks und Gluonen möglich sein.

Eine Beschreibung der theoretischen Grundlagen zur Untersuchung der Spinstruktur des Nukleons erfolgt in Kapitel 2. Das COMPASS-II Experiment ist ein "Fixed-

<sup>&</sup>lt;sup>2</sup>EMC = European Muon Collaboration

<sup>&</sup>lt;sup>3</sup>CERN = Conseil Européen de la Recherche Nucleaire

<sup>&</sup>lt;sup>4</sup>COMPASS = Common Muon and Proton Apparatus for Structure and Spectroscopy

<sup>&</sup>lt;sup>5</sup>DVCS = Deep Inelastic Compton Scattering

Target-Experiment" und besteht aus mehreren Detektorkomponenten. Der Aufbau des Spektrometers zur Vermessung exklusiver Prozesse wird in Kapitel 3 erläutert.

Für die Verarbeitung der Detektorsignale werden teilweise sehr hohe Ansprüche an die Auslese-Elektronik gestellt. Dafür werden oftmals FPGAs<sup>6</sup> [12] eingesetzt. Dabei handelt es sich um integrierte Schaltkreise, in denen eine spezifische Funktion einprogrammiert werden kann. Vor allem ihre freie Rekonfigurierbarkeit macht FPGAs für den Einsatz in Teilchenphysik-Experimenten interessant, da in kürzester Zeit eine Zuschneidung auf sehr spezielle Aufgaben erfolgen kann. Im Rahmen dieser Diplomarbeit wird eine FPGA-Firmware zur Detektorauslese entwickelt, die auf einem Xilinx Virtex-5 FPGA [13] implementiert wird. Dieser befindet sich auf der Hauptplatine des in Freiburg entwickelten GANDALF<sup>7</sup>-Moduls, welches für die Auslese und Echtzeitanalyse von Detektorsignalen entwickelt wurde. Einen Überblick der vielseitigen Einsatzmöglichkeiten des Moduls befindet sich in Kapitel 4.

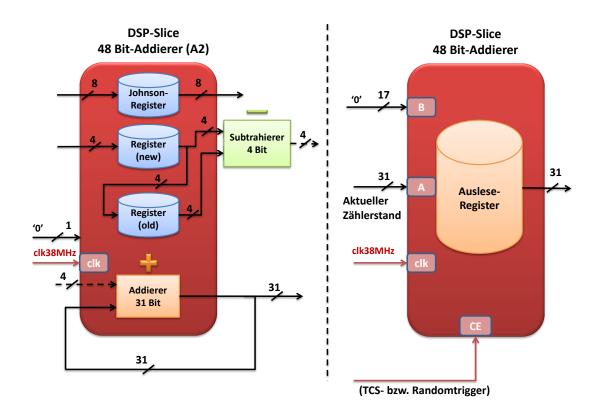

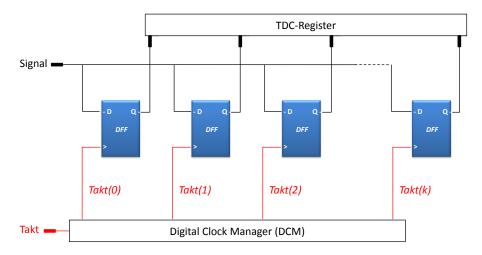

Die FPGA-Firmware beinhaltet einen 96-Kanal-Scaler, welcher digitale Signale bis über 500 MHz fehlerfrei zählen kann. Wie in Kapitel 5 näher erläutert, basiert der Mechanismus auf dem Johnson-Code, der einen fehlerfreien Zähl- und Auslesevorgang ermöglicht. Außerdem enthält das FPGA-Design die Funktion, sehr präzise Zeitintervalle besser als 100 ps zu vermessen, womit eine Strahlanalyse auch auf sehr kleinen Zeitabschnitten erfolgen kann. Diese Aufgabe übernimmt ein Time-to-Digital Converter (TDC).

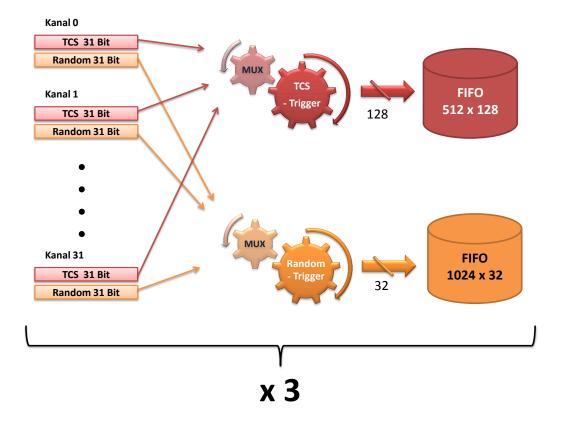

Beide Komponenten werden kombiniert und wie in Kapitel 6 erklärt auf einem einzigen Xilinx Virtex-5 FPGA implementiert. Für die Strahlanalyse wird ein Pseudo-Randomtrigger benötigt, dessen Logik entwickelt und ebenfalls in die FPGA-Firmware integriert wird. Sowohl Scaler als auch TDC müssen in das COMPASS Datennahme-System integriert werden. Unabhängig davon ist eine Auslese der zufällig getriggerten Daten für das Beam-Monitoring-System vorgesehen.

Ziel dieser Arbeit ist die Entwicklung eines Systems zur voll automatisierten Strahlanalyse in Echtzeit. Damit soll eine Überwachung und Kontrolle verschiedener Strahlattribute, beispielsweise der Strahlrate ermöglicht werden. Das System soll vor allem dazu in der Lage sein, Systematiken im Strahl aufzudecken, um so die Strahlqualität beziehungsweise die Güte des Teilchenstrahls beurteilen zu können.

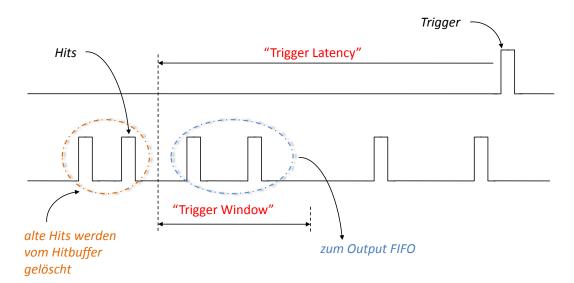

In Kapitel 7 werden erste Messungen des Teilchenstrahls vorgestellt. Das FPGA-Design kam erstmals im Rahmen der DVCS-Messungen im Herbst 2012 zur Auslese eines Detektors mit szintillierenden Fasern (FI02) zum Einsatz. Hierbei handelt es sich um einen Detektor der sich vor dem Target befindet. Damit werden Daten für die Darstellung verschiedener Strahlattribute gewonnen. Mit einer Analyse werden während des Experiments in Echtzeit Graphen und Histogramme erzeugt. Dazu gehören beispielsweise das Strahlprofil und der Strahlschwerpunkt beziehungsweise die Strahlrate in Abhängigkeit der Zeit. Die dazugehörigen Daten werden mit der Scaler-Komponente der FPGA-Firmware gewonnen. Die TDC-Komponente ermöglicht außerdem eine Kreuzkorrelation der Zeitmarken der auf dem Eingangssignal gemessenen Hits, womit die zeitliche Zufälligkeit der Strahlteilchen beziehungsweise Systematik auf kleinen Zeitabschnitten beurteilt werden kann.

<sup>&</sup>lt;sup>6</sup>FPGA = Field Programmable Gate Array

<sup>&</sup>lt;sup>7</sup>GANDALF = Generic Advanced Numerical Device for Analytic and Logic Functions

4 \_\_\_\_\_\_ 1. Einleitung

# 2. Physikalische Grundlagen

In diesem Kapitel wird ein kurzer Abriss der theoretischen Grundlagen und Konzepte zur Untersuchung der Spinstruktur des Nukleons dargelegt. Dies ist Forschungsgebiet des COMPASS-II Experiments, an dem Streuexperimente mit hochenergetischen Myonen durchgeführt werden. Grundlegend für die Erforschung der Spinstruktur des Nukleons sind die generalisierten Parton-Verteilungsfunktionen (GPD<sup>1</sup>), die über tief-inelastische Lepton-Nukleon-Streuung vermessen werden.

Diese Beschreibungen machen es möglich, Gesamtdrehimpulsbeiträge der einzelnen Konstituenten, also Gluonen und Quarks, des Nukleons direkt zu bestimmen und somit Aufschluss über die Substruktur des Nukleons zu erhalten. Es wird die tief-virtuelle Compton-Streuung als vielversprechende Methode zur Untersuchung der Substruktur des Nukleons vorgestellt. Die wesentlichen Konzepte dieser Theorien werden in diesem Kapitel kurz erläutert.

<sup>&</sup>lt;sup>1</sup>GPD = Generalized Parton Distributions

## 2.1 Der Spin des Nukleons

Der Spin ist eine vektorwertige Größe und lässt sich semiklassisch als intrinsischer Drehimpuls von Teilchen verstehen, welcher eigentlich eine quantenmechanische Observable ist und in Einheiten von  $\hbar$  (Planck-Konstante) angegeben wird. Aus Ableitungen der Drehimpuls-Eigenzustände  $|jm\rangle^2$  im Hilbertraum ergibt sich neben ganzzahligen Werten für j auch die Möglichkeit, halbzahlige Werte, also halbzahlige Drehimpulse, anzunehmen. Der Bahndrehimpuls-Operator führt jedoch nur zu ganzzahligen Werten für j.

Dies stellt nicht nur eine mathematische Möglichkeit dar, sondern sie ist auch von physikalischer Relevanz. In der Tat existieren intrinsische Drehimpulse von Teilchen, welche auch durch diese Lösungen beschrieben werden können [14].

Das Nukleon wird von Quarks beziehungsweise Antiquarks (Spin  $\frac{1}{2}\hbar$ ) und Gluonen (Spin  $1\hbar$ ) gebildet. Der Gesamtspin des Nukleons kann als Addition der totalen Drehimpulse  $J_q$  und  $J_g$  der Quarks und Gluonen geschrieben werden [15]:

$$\frac{J}{\hbar} = \frac{1}{2} = J_q + J_g. \tag{2.1}$$

Damit ergibt sich für den Gesamtspin:

$$\frac{S}{\hbar} = \frac{1}{2} = \frac{1}{2}\Delta\Sigma + \Delta G + L_q + L_g,\tag{2.2}$$

wobei  $\Delta\Sigma$  der Beitrag der Quarks und Antiquarks,  $\Delta G$  der Beitrag der Gluonen und  $L_q$ ,  $L_g$  die Drehimpulsbeiträge der Nukleonkonstituenten sind.

Nun ist aus früheren Experimenten bekannt, dass der Beitrag der Quarks und Antiquarks  $\Delta\Sigma \approx 0,3$  und der der Gluonen  $|\Delta G| \approx 0,2-0,3$  ist [16, 17]. Dabei ist man sich über die Größe der Gesamtdrehimpulse  $J_q$  und  $J_g$  noch weitestgehend im Unklaren

Ein möglicher Zugang zu den Größen  $J_q$  und  $J_g$ , bieten die GPDs (siehe Abschnitt 2.4). Sie werden im COMPASS-II Experiment unter anderem über DVCS vermessen. Durch die Summenregel von X. Ji [18] lässt sich ein Zusammenhang zwischen den Gesamtdrehimpulsen  $J_f^3$  der Nukleonkonstituenten und den GPDs  $H^f$  beziehungsweise  $E^f$  herstellen (siehe Abschnitt 2.4.2):

$$J_f = \frac{1}{2} \lim_{t \to 0} \int_{-1}^1 dx \ x \left[ H^f(x, \xi, t) + E^f(x, \xi, t) \right]. \tag{2.3}$$

<sup>&</sup>lt;sup>2</sup>Dabei bezeichnet j die dem Betrag eines Drehimpulses  $\sqrt{\vec{L}^2}$  zugeordnete Quantenzahl und m die der dritten Komponente  $L_3$ .

$<sup>^3</sup>f$  bezeichnet den Quarkflavour =  $u, \bar{u}, d, \bar{d}, s, \bar{s}$

### 2.2 Tief-inelastische Lepton-Nukleon-Streuung

Die innere Zusammensetzung des Nukleons lässt sich über tief-inelastische Lepton-Nukleon-Streuung (DIS<sup>4</sup>) untersuchen, wobei ein einfliegendes leptonisches Teilchen l an einem Konstituentenquark des Nukleons gestreut wird. Hierbei wird ein virtuelles Photon  $\gamma^*$  ausgetauscht (siehe Abbildung 2.1). Um Aufschluss über die inneren Wechselwirkungspotenziale zu bekommen, müssen die dabei auftretenden Viererimpulsüberträge

$$q^{2} = (P_{l} - P_{l'})^{2} = 2m_{l}^{2}c^{2} - 2\left(\frac{E_{l}E_{l'}}{c^{2}} - \vec{p_{l}} \cdot \vec{p_{l'}}\right) = -Q^{2},$$

(2.4)

die durch virtuelle Photonen vermittelt werden, sehr groß sein. Die Variablen werden in Tabelle 2.1 definiert.

Das Nukleon kann in einen angeregten Zustand umgewandelt oder durch Hadronisierung in mehrere stark wechselwirkende Teilchen aufgebrochen werden:

$$l + N \to l' + X. \tag{2.5}$$

Man unterscheidet hierbei zwischen inklusiven, semi-inklusiven und exklusiven Endzuständen. Im Vergleich zur inklusiven Streuung, werden bei der semi-inklusiven und exklusiven Streuung außer dem Lepton l noch mindestens ein Hadron beziehungsweise alle Teilchen im Endzustand nachgewiesen.

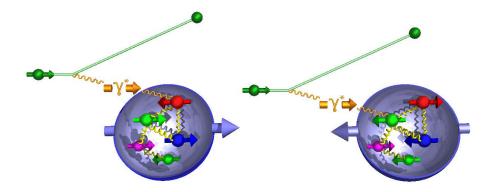

Abbildung 2.1: Semi-inklusive tief-inelastischen Streuung [19].

<sup>&</sup>lt;sup>4</sup>DIS = Deep Inelastic Scattering

| Variable                                                                                                                                       | Beschreibung                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| $P_l = (E_l, \vec{p_l})$ $P_{l'} = (E_{l'}, \vec{p_{l'}})$                                                                                     | Viererimpuls des einlaufenden Leptons<br>Viererimpuls des auslaufenden Leptons           |

| $P_N = (E_N, \vec{p_N}) \stackrel{lab}{=} (M, 0, 0, 0)$ $q = P_l - P_{l'}$                                                                     | Viererimpuls des Protons<br>Viererimpuls des virtuellen Photons                          |

| $ \nu = \frac{P_N \cdot q}{M} \stackrel{lab}{=} E_l - E_{l'} $ $ y = \frac{P_N \cdot q}{P_N \cdot P_l} = \frac{\nu}{E_l} $                     | Energieverlust des gestreuten Leptons<br>Relativer Energieverlust des gestreuten Leptons |

| $Q^{2} = -q^{2} \stackrel{lab}{\approx} 4E_{l}E_{l'} \cdot \sin^{2}\frac{\vartheta}{2}$ $x_{Bj} = \frac{Q^{2}}{2P_{N}q} = \frac{Q^{2}}{2M\nu}$ | negatives Quadrat des Viererimpulses des<br>virtuellen Photons<br>Bjorken-Skalenvariable |

Tabelle 2.1: Kinematische Variablen der tief-inelastische Streuung [20].

Die Skalenvariable  $x_{Bj}$  kann im sogenannten "Infinite Momentum Frame" (IMF) als Bruchteil des von einem Parton getragenen Nukleon-Viererimpulses interpretiert werden, bevor das virtuelle Photon absorbiert wird [21]. Das IMF bezeichnet ein sehr schnell bewegtes Bezugssystem in dem die transversalen Impulse und die Ruhemassen der Konstituenten vernachlässigt werden. Die Wechselwirkungen des einfliegenden Leptons mit einzelnen Konstituenten des Nukleons kann als elastisch angesehen werden, sofern es im Nukleon währenddessen zu keinen internen Wechselwirkungen kommt.

### 2.3 Die Parton-Verteilungsfunktionen

Der DIS-Prozess kann im sogenannten Bjorken-Limit mit

$$Q^2, \nu \to \infty,$$

(2.6)

in einen weichen hadronischen und einen harten leptonischen Anteil aufgeteilt werden [22, 23]:

$$\frac{d^2\sigma}{d\Omega dE_{l'}} = \frac{\alpha_{\rm em}^2}{Q^4} \frac{E_{l'}}{E_l} L_{\mu\nu} W^{\mu\nu}, \tag{2.7}$$

wobei  $L_{\mu\nu}$  den leptonische Tensor, der die Streuung des virtuellen Photons an einem Quark beschreibt und  $W^{\mu\nu}$  den hadronischen Tensor bezeichnet, der die interne Struktur des Nukleons beschreibt.  $\alpha_{\rm em}$  bezeichnet die Feinstrukturkonstante, welche die Stärke der elektromagnetischen Kopplung angibt.

Im Gegensatz zum leptonische Tensor  $L_{\mu\nu}$ , der in pertubativer Quantenelektrodynamik (pQED) berechnet werden kann, ist für den hadronischen Tensor nur eine Parametrisierung durch Parton-Verteilungsfunktionen (PDFs<sup>5</sup>) möglich, die experimentell bestimmt werden müssen. Das Tensorprodukt lässt sich mit folgender Relation noch weiter separieren:

$$L_{\mu\nu}W^{\mu\nu} = \left[ L_{\mu\nu}^{(S)}(x_{Bj}) \ W^{\mu\nu(S)}(x_{Bj}) - L_{\mu\nu}^{(A)}(x_{Bj}, \ \vec{s}) \ W^{\mu\nu(A)}(x_{Bj}, \ \vec{S}) \right]. \tag{2.8}$$

<sup>&</sup>lt;sup>5</sup>PDF = Parton Distribution Functions

Bei einem mit (S) markierten Tensor handelt es sich um einen symmetrischen, spinunabhängigen Anteil. Dieser kann durch dimensionslose Strukturfunktionen  $F_1(x_{Bj})$  und  $F_2(x_{Bj})$ , welche die Streuung an unpolariserten Nukleonen beschreiben, ausgedrückt werden. Bei einem mit (A) markierten Tensor handelt es sich um einen antisymmetrischen, spinabhängigen Anteil. Dieser kann durch die Strukturfunktionen  $g_1(x_{Bj})$  und  $g_2(x_{Bj})$  ausgedrückt werden, die die Streuung an polariserten Nukleonen beschreiben [24]. Die Größen  $\vec{s}$ ,  $\vec{S}$  bezeichnen den Lepton- beziehungsweise Nukleonspin.

#### 2.3.1 Unpolarisierte Parton-Verteilungsfunktionen

Die Strukturfunktionen  $F_1$  und  $F_2$  können durch unpolarisierte Parton-Verteilungsfunktionen ausgedrückt werden, wobei über alle Quarkflavour f summiert wird [21]:

$$F_1(x_{Bj}) = \frac{1}{2} \sum_f e_f^2 q_f(x_{Bj}), \qquad F_2(x_{Bj}) = x_{Bj} \sum_f e_f^2 q_f(x_{Bj}).$$

(2.9)

Dabei bezeichnet  $e_f$  die elektrische Ladung der Quarks<sup>6</sup>, sowie  $q_f(x_{Bj})dx_{Bj}$  die Wahrscheinlichkeit, ein Quark mit Flavour f und Impulsbruchteil im Intervall  $[x_{Bj}, x_{Bj} + dx_{Bj}]$  zu finden. Der Zusammenhang für  $F_1$  ergibt sich aus  $F_2$  und der sogenannten Callan-Gross-Beziehung, die für Dirac-Teilchen mit Spin  $\hbar/2$  gilt [21],

$$2x_{Bj}F_1(x_{Bj}) = F_2(x_{Bj}). (2.10)$$

# 2.3.2 Die longitudinal polarisierten Parton-Verteilungsfunktionen

PDFs erlauben Rückschlüsse auf die Helizitätsverteilung der Quarks. Bei tiefinelastischer Lepton-Nukleon-Streuung kann das virtuelle Photon wegen der Erhaltung der Helizität nur dann absorbiert werden, wenn die Helizität des streuenden Quarks entgegengesetzt ist (siehe Abbildung 2.2). Man bekommt somit einen Einblick in die Verteilung, indem longitudinal polarisierte Leptonen an einem zur Bewegungsrichtung dieser Leptonen parallel beziehungsweise antiparallel polarisierten Target gestreut werden.

Die Helizitätsverteilungsfunktionen erhält man mittels Subtraktion der Funktionen  $q_f^{\rightleftarrows}(x_{Bj})$  von  $q_f^{\rightrightarrows}(x_{Bj})$ :

$$\Delta q_f(x_{Bj}) = q_f^{\Rightarrow}(x_{Bj}) - q_f^{\rightleftharpoons}(x_{Bj}), \qquad (2.11)$$

Dabei geben  $q_f^{\rightrightarrows}(x_{Bj})$  beziehungsweise  $q_f^{\rightleftarrows}(x_{Bj})$  die Wahrscheinlichkeiten dafür an, ein Quark mit gleicher beziehungsweise entgegengesetzter Helizität, bezogen auf das Nukleon, zu finden.

$<sup>6</sup>e_f = \pm \frac{1}{3}e, \pm \frac{2}{3}e$

Abbildung 2.2: Streuung longitudinal polarisierter Leptonen an polarisierten Protonen. Im linken Bild sind Lepton und Proton gleich polarisiert. Rechts sind diese entgegengesetzt polarisiert [25].

Wenn nun über alle Quarkflavour summiert und über  $x_{Bj}$  integriert wird, erhält man den Helizitätsbeitrag der Quarks und der Antiquarks ( $\Delta\Sigma$  in Gleichung 2.12). Eine Darstellung der helizitätsabhängigen Strukturfunktion  $g_1$  (siehe Gleichung 2.13) ist analog zu den Gleichungen in 2.9 mittels Gleichung 2.11 möglich. Eine entsprechende Darstellung für  $g_2$  durch PDFs im Partonmodell existiert nicht.

$$\Delta\Sigma = \sum_{f} \int_{0}^{1} \Delta q_f(x_{Bj}) dx_{Bj}, \qquad (2.12)$$

$$g_1(x_{Bj}) = \frac{1}{2} \sum_f e_f^2 \, \Delta q_f(x_{Bj}).$$

(2.13)

## 2.4 Generalisierte Parton-Verteilungen

Generalisierte Parton-Verteilungen (GPDs) wurden in theoretischen Arbeiten von Müller [26], Radyushkin [27] und Ji [18] eingeführt. Für DVCS (siehe Abschnitt 2.5) kann die Faktorisierung in einen harten und einen weichen Anteil, wie im Kapitel 2.2 beschrieben, angewendet werden. DVCS ist ein Prozess bei dem die wechselwirkenden Nukleonkonstituenten nicht zerstört werden, das heißt das Nukleon bleibt intakt. Will man ein vollständiges Bild der dreidimensionalen Struktur des Nukleon erhalten, so ist dies nur über solche Prozesse möglich, da dann Wechselwirkungen der Konstituenten des Nukleons untereinander vermessen werden können.

Durch die Einführung generalisierter Parton-Verteilungen ist eine dreidimensionale Vereinigung über sowohl longitudinale Impulse als auch transversale Positionen der Partonen möglich. Dies stellt bis heute die einzige Möglichkeit dar, Informationen über die Gesamtdrehimpulsbeiträge der Quarks und Gluonen zum Spin des Nukleons zu erhalten.

#### 2.4.1 Kinematische Variablen

Im Folgenden werden weitere zur Beschreibung der GPDs wichtige Variablen erläutert [28]:

$$t = (p - p')^2 = (q - q')^2 := -\Delta^2,$$

(2.14)

$$\xi = x_{Bj} \frac{1 + \frac{\Delta^2}{2Q^2}}{2 - x_{Bj} + x_{Bj} \frac{\Delta^2}{Q^2}} \approx \frac{x_{Bj}}{2 - x_{Bj}}.$$

(2.15)

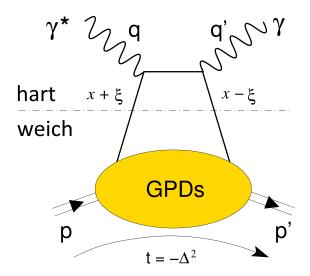

Hierbei ist t die Mandelstam-Variable, die den Viererimpuls-Übertrag auf das Nukleon angibt. q bezeichnet den Viererimpuls des virtuellen Photons  $\gamma^*$  sowie q' den des auslaufenden Photons  $\gamma$  (verlgeiche Abbildung 2.3).  $\xi$  ist die sogenannte Skewness<sup>7</sup>-Variable, die von  $x_{Bj}$  abhängig ist.

Das Quark besitzt nach der Emission eines reellen Photons einen um  $2\xi$  veränderten Viererimpuls  $(p=x+\xi,\,p'=x-\xi)$ . Die Größe  $\xi$  kann als Bruchteil des Impulsübertrags bezüglich der charakteristischen Richtung des unendlichen Impulses (IMF) betrachtet werden.  $\xi=0$  bedeutet, dass kein longitudinaler Impuls übertragen wird. Für  $\xi\neq 0$  hat der Impulsübertrag auch eine nichtverschwindende Komponente parallel zum Impuls des virtuellen Photons.

Abbildung 2.3: Handbag-Diagramm der tief-virtuellen Compton-Streuung [29]. Die Beschreibung des weichen Anteils erfolgt durch GPDs.

Wie bereits erwähnt ist für die Beschreibung des weichen hadronischen Anteils des Streuprozesses eine Parametrisierung durch Parton-Verteilungsfunktionen möglich. Im Folgenden werden vier GPDs  $(H, \tilde{H}, E, \tilde{E})$  eingeführt, die von den kinematischen Variablen  $t, \xi$  und x abhängig sind und sich bezüglich der Quark-Helizitätserhaltung und der Nukleon-Helizitätserhaltung unterscheiden. Dabei sind H und  $\tilde{H}$  Nukleon-Helizität-erhaltende und E beziehungsweise  $\tilde{E}$  Nukleon-Helizitätumkehrende GPDs. Die Abhängigkeit von der Quark-Helizität wird in Tabelle 2.2 durch  $(\tilde{\ })$  unterschieden.

<sup>&</sup>lt;sup>7</sup>engl.: Schiefe

|                                    | Nukleon-Helizität<br><b>erhaltend</b> | Nukleon-Helizität<br>umkehrend |

|------------------------------------|---------------------------------------|--------------------------------|

| Quark-Helizitäts <b>unabhängig</b> | $H^{q,g}$                             | $E^{q,g}$                      |

| Quark-Helizitäts <b>abhängig</b>   | $	ilde{H}^{q,g}$                      | $	ilde{E}^{q,g}$               |

Tabelle 2.2: Übersicht über die vier GPDs H,  $\tilde{H}$ , E und  $\tilde{E}$ .

# 2.4.2 Zusammenhang der GPDs mit bekannten Verteilungen

Im Grenzfall lassen sich GPDs auf PDFs zurückführen. Diesen Spezialfall nennt man "Vorwärtslimit" und es gelten folgende Relationen:

$$t = 0 \quad \text{und} \quad \xi = 0.$$

(2.16)

In diesem Grenzfall sind Vierer-Impuls und Helizität des Nukleons im Anfangsund Endzustand gleich. Es ist möglich, einen Zusammenhang zwischen den GPDs und den schon bekannten PDFs (vergleiche Abschnitt 2.3) herzustellen [30]:

für

$$x > 0$$

:  $H^f(x, 0, 0) = q_f(x)$ ,  $\tilde{H}^f(x, 0, 0) = \Delta q_f(x)$ , (2.17)

für

$$x < 0$$

:  $H^f(x, 0, 0) = -\bar{q}_f(-x)$ ,  $\tilde{H}^f(x, 0, 0) = \Delta \bar{q}_f(-x)$ . (2.18)

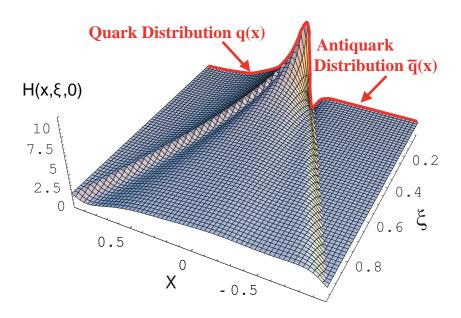

Für x > 0 werden die GPDs  $H^f$  und  $\tilde{H}^f$  als Quark- beziehungsweise für x < 0 als Antiquark-Verteilungsfunktionen interpretiert. In Abbildung 2.4 ist die GPD  $H^u(x, \xi, t = 0)$  in Abhängigkeit von x und  $\xi$  dargestellt.

Desweiteren besteht neben den Beziehungen der GPDs zu den PDFs ein Zusammenhang zwischen den ersten Momenten der GPDs und den elastischen Formfaktoren des Nukleons [18]:

$$\sum_{f} z_{f} \int_{-1}^{+1} dx H^{f}(x, \xi, t) = F_{1}(t), \qquad \sum_{f} z_{f} \int_{-1}^{+1} dx \tilde{H}^{f}(x, \xi, t) = G_{A}(t),$$

$$\sum_{f} z_{f} \int_{-1}^{+1} dx E^{f}(x, \xi, t) = F_{2}(t), \qquad \sum_{f} z_{f} \int_{-1}^{+1} dx \tilde{E}^{f}(x, \xi, t) = H_{A}(t),$$

(2.19)

wobei  $F_1(t)$ ,  $F_2(t)$ ,  $G_A(t)$  und  $H_A(t)$  die elastischen Dirac-, Pauli, Axial- und Pseudo-Skalaren Formfaktoren bezeichnen. Die zweiten Momente der GPDs führen auf den gesamten Drehimpuls der Quarks. Dieser Zusammenhang ist als Jis Summenregel bekannt (siehe Gleichung 2.3).

Abbildung 2.4: Simulation der GPD  $H(x, \xi, t = 0)$  für das u-Quark [31]. Die rote Linie kennzeichnet den Verlauf der unpolarisierten PDFs für Quarks (x > 0) und Antiquarks (x < 0). Der Bereich  $|x| \ge \xi$  ist über DVCS zugänglich.

#### 2.4.3 Stoßparameterabhängige Parton-Verteilungen

Für  $\xi=0$  kann eine besonders einfache physikalische Interpretation der GPDs als Wahrscheinlichkeitsdichte angegeben werden. Damit kommt es nur zu transversalen Impulsüberträgen:

$$t = -\Delta^2 = -\Delta_L^2 - \Delta_\perp^2 = -\Delta_\perp^2. \tag{2.20}$$

Die Fouriertransformierte der GPD  $H(x,0,-\Delta_{\perp}^2)$  beschreibt die räumliche Verteilung der Partonen bei einem transversalen Abstand  $|\vec{b}_{\perp}|$  vom Impulsschwerpunkt des Nukleons in Abhängigkeit des Impulsbruchteils x [32]:

$$q_f(x, \vec{b}_\perp) = \int \frac{d^2 \Delta_\perp^2}{(2\pi)^2} e^{-i\Delta_\perp \cdot \vec{b}_\perp} H^f(x, 0, -\Delta_\perp^2).$$

(2.21)

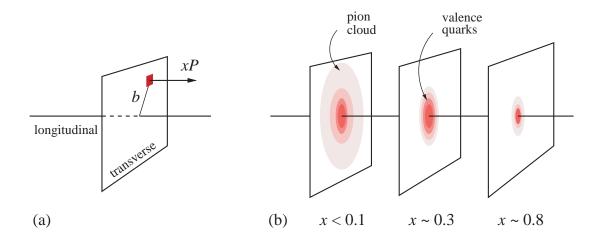

Integriert man zudem über  $b_{\perp}$ , würde man die gewöhnlichen PDFs erhalten. Mit der stoßparameterabhängigen Funktion  $q_f(x, \vec{b}_{\perp})$  lässt sich wie in Abbildung 2.5 veranschaulicht, eine "Tomografie" des Nukleons erstellen.

Abbildung 2.5: Nukleon-Tomografie [33]: (a) Die Fouriertransformierte der GPD  $H(x,0,-\Delta_{\perp}^2)$  beschreibt die b-Verteilung der Partonen mit Longitudinalimpuls xP bei konstantem x. Hierbei ist  $b=|\vec{b}_{\perp}|$  der Abstand der Partonen zum Impulsschwerpunkt in der Transversalebene. (b) Für verschiedene Impulsbruchteile x ist die Ortsverteilung der Partonen dargestellt. Die Verteilung wird bei kleinen x von Seequarks und Gluonen, sowie bei  $x\approx 0,3$  von Valenzquarks dominiert. Für  $x\to 1$  wird die Verteilung nur durch das aktiv wechselwirkende Parton bestimmt.

## 2.5 Tief-virtuelle Compton-Streuung

Die Tief-virtuelle Compton-Streuung bietet eine vielversprechende Methode, Informationen über die innere Struktur des Nukleons zu erhalten. Hierbei wird ein Lepton l an einem Nukleon gestreut. Das Nukleon, welches dabei unversehrt bleibt, emittiert ein reelles Photon  $\gamma$ :

$$l + N \to l' + N' + \gamma. \tag{2.22}$$

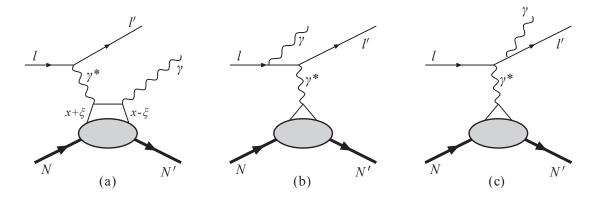

Abbildung 2.6: Leptoproduktion reeller Photonen durch Prozesse führender Ordnung.

(a) DVCS, (b) und (c) Bethe-Heitler-Prozess [19].

In Abbildung 2.6 (a) wird der DVCS-Prozess dargestellt. Ein Quark mit longitudinalem Impulsbruchteil  $x + \xi$  absorbiert ein virtuelles Photon  $\gamma^*$  mit Virtualität

$Q^2 = -q^2$  (vergleiche Tabelle 2.1) und emittiert ein reelles Photon  $\gamma$ . Da der in Abbildung 2.6 (b) beziehungsweise (c) dargestellte Bethe-Heitler-Prozess (BH-Prozess) den gleichen Anfangs- und Endzustand wie der DVCS-Prozess aufweist, interferieren die Amplituden beider Prozesse miteinander. Somit lässt sich der differentielle Wirkungsquerschnitt schreiben als [19]:

$$\frac{d\sigma(lN \to l'N'\gamma)}{dxdQ^2d|t|d\phi} \propto |\tau_{BH}|^2 + |\tau_{DVCS}|^2 + \underbrace{\tau_{DVCS}\tau_{BH}^* + \tau_{DVCS}^*\tau_{BH}^*}_{I}, \tag{2.23}$$

wobei  $\phi$  den azimutalen Winkel zwischen der durch die Richtung des ein- beziehungsweise auslaufenden Leptons aufgespannten Streuebene und der durch das virtuelle und reelle Photon aufgespannten Produktionsebene darstellt. Die Streuamplitude des jeweiligen Prozesses ist mit  $\tau$  bezeichnet. Wie in Abbildung 2.6 ersichtlich ist der Bethe-Heitler-Prozess rein elektromagnetisch. Dieser Prozess kann in der Quantenelektrodynamik berechnet werden, sofern man die elektromagnetischen Formfaktoren kennt. Diese können jedoch vermessen werden. Aus dem Bethe-Heitler-Prozess kann für die Bestimmung der GPDs keinerlei Information herangezogen werden. Im Gegensatz dazu kann das aus einem DVCS-Prozess entstandene reelle Photon  $\gamma$  zur Bestimmung der GPDs benutzt werden, da es durch die Wechselwirkung mit dem Nukleon entsteht. Der Interferenzterm I kann herangezogen werden, um Informationen über den Real- und den Imaginärteil der DVCS-Amplitude zu erhalten.

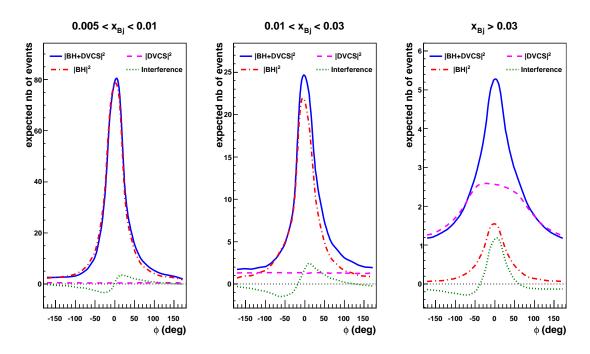

Die Zusammensetzung des Wirkungsquerschnitts ist stark vom kinematischen Bereich abhängig. Für  $x_{Bj}>0,03$  setzt sich dieser hauptsächlich aus der DVCS-Amplitude zusammen:

$$\frac{d\sigma(lN \to l'N'\gamma)}{dxdQ^2d|t|d\phi} \propto |\tau_{DVCS}|^2, \tag{2.24}$$

wohingegen der BH-Prozess für sehr kleine Werte von  $x_{Bj}$  dominant ist (siehe Abbildung 2.7).

Durch die Messung der Strahl-Ladungs-Asymmetrie, (BCA<sup>8</sup>) ist eine Möglichkeit gegeben, DVCS-Prozesse zu untersuchen. Der von den BH-Prozessen stammende Beitrag ist unabhängig von der Ladung des einfliegenden Leptons, jedoch nicht der von den DVCS-Prozessen stammende, welcher sein Vorzeichen wechselt. Dadurch lässt sich der Realteil der DVCS-Amplitude durch Subtraktion der jeweils gemessenen Wirkungsquerschnitte für unterschiedlich geladene Leptonen extrahieren.

$$\frac{d\sigma(l^+N \to l^{+'}N'\gamma)}{dxdQ^2d|t|d\phi} - \frac{d\sigma(l^-N \to l^{-'}N'\gamma)}{dxdQ^2d|t|d\phi} \propto \tau_{BH} Re(\tau_{DVCS}). \tag{2.25}$$

$\tau_{BH}$  ist nur von den elastischen Nukleonformfaktoren abhängig. Sie ist somit eine wohlbekannte Größe. Misst man nun mit Strahlung entgegengesetzter Helizität und gleicher Ladung, lässt sich der Imaginärteil der DVCS-Amplitude ermitteln:

$$\frac{d\sigma(l^{\uparrow}N \to l^{\uparrow'}N'\gamma)}{dxdQ^{2}d|t|d\phi} - \frac{d\sigma(l^{\downarrow}N \to l^{\downarrow'}N'\gamma)}{dxdQ^{2}d|t|d\phi} \propto Im(\tau_{DVCS}). \tag{2.26}$$

<sup>&</sup>lt;sup>8</sup>BCA = Beam Charge Asymmetry

Abbildung 2.7: Ergebnisse aus einer Monte-Carlo-Simulation. Die Wechselwirkungsbeiträge der BH- und DVCS-Prozesse für die Reaktion  $\mu p \to \mu p \gamma$  sind in Abhängigkeit des Winkels  $\phi$  für verschiedene  $x_{Bj}$  aufgetragen [29].

Da der Myonstrahl im COMPASS-II Experiment durch den maximal Paritätsverletzenden Zerfall von geladenen Pionen  $\pi^{\pm}$  und Kaonen  $K^{\pm}$  zustande kommt, ist dieser natürlicherweise schon polarisiert. Durch die BCA-Messung gewinnt man mit Hilfe folgender Relationen Informationen über die GPD  $\mathcal{H}$ :

$$S = \frac{d\sigma(l^{+\downarrow}N \to l^{+\downarrow'}N'\gamma)}{dxdQ^2d|t|d\phi} + \frac{d\sigma(l^{-\uparrow}N \to l^{-\uparrow'}N'\gamma)}{dxdQ^2d|t|d\phi} \propto Im(F_1\mathcal{H})\sin(\phi), \quad (2.27)$$

$$S = \frac{d\sigma(l^{+\downarrow}N \to l^{+\downarrow'}N'\gamma)}{dxdQ^2d|t|d\phi} + \frac{d\sigma(l^{-\uparrow}N \to l^{-\uparrow'}N'\gamma)}{dxdQ^2d|t|d\phi} \propto Im(F_1\mathcal{H})\sin(\phi), \qquad (2.27)$$

$$\mathcal{D} = \frac{d\sigma(l^{+\downarrow}N \to l^{+\downarrow'}N'\gamma)}{dxdQ^2d|t|d\phi} - \frac{d\sigma(l^{-\uparrow}N \to l^{-\uparrow'}N'\gamma)}{dxdQ^2d|t|d\phi} \propto Re(F_1\mathcal{H})\cos(\phi). \qquad (2.28)$$

Hierbei ist  $\mathcal{S}$  die Summe und  $\mathcal{D}$  die Differenz der gemessenen Wirkungsquerschnitte.

Durch Integration beziehungsweise Analyse der Winkelabhängigkeit lassen sich Kombinationen verschiedener Quark-GPDs bestimmen. So erhält man beispielsweise mittels Analyse der Summe  $\mathcal{S}$  den Imaginärteil des Compton-Formfaktors  $\mathcal{H}$ . Integriert man über den Winkel  $\phi$ , erhält man Aufschluss über die transversale Ausdehnung des Nukleons. Der Differenzterm  $\mathcal{D}$  enthält den Realteil des Compton-Formfaktors  $\mathcal{H}$ . Dieser ist in führender Ordnung durch eine Faltung der GPD H mit einer die harte Quark-Photon-Wechselwirkung  $\gamma^*q$  beschreibende Funktion gegeben.

# 3. Das COMPASS-II Experiment

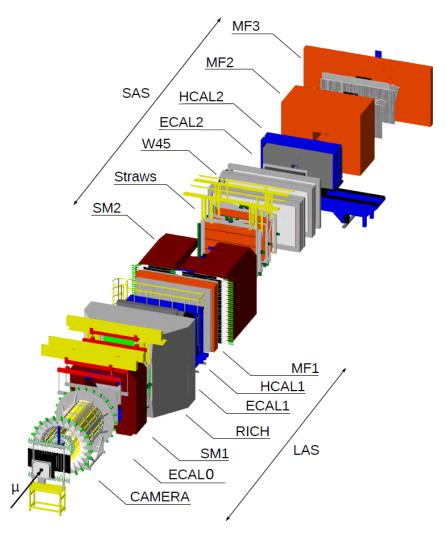

Das COMPASS-II Experiment befindet sich auf dem nördlichen CERN-Gelände in der Nähe von Genf. Es ist ein Fixed-Target-Experiment zur Erforschung der Nukleon-Spinstruktur und der Hadronspektroskopie, bei dem hochenergetische Myonen beziehungsweise Hadronen auf ruhende Nukleonen treffen. Es zeichnet sich dabei durch seine hohe Flexibilität bezüglich Einbindung seiner Spektrometerkomponenten aus. Der Aufbau des COMPASS-II Experiments besteht aus drei Teilen. Der erste Bereich befindet sich vor dem Target. Dort werden Impulse und Lage der einlaufenden Teilchen mittels Spurdetektoren vermessen. Der zweite Bereich, dort wo sich das Target befindet, kann als Wechselwirkungszone bezeichnet werden. Daran anschließend befindet sich das COMPASS-II-Spektrometer, in welchem auslaufende Teilchen vermessen werden. Das Spektrometer ist zweistufig aufgebaut und besteht aus einem Bereich zum Nachweis von Teilchen, die unter großen Winkeln bis 180 mrad gestreut werden und aus einem Bereich in dem auslaufende Teilchen bis 30 mrad nachgewiesen werden können.

Im Folgenden werden sowohl die wichtigsten Komponenten des Spektrometers, die Führung des Teilchenstrahls, als auch die Datennahme am COMPASS-II Experiment vorgestellt. Für eine detailliertere Beschreibung des Experiments sei auf [34] verwiesen.

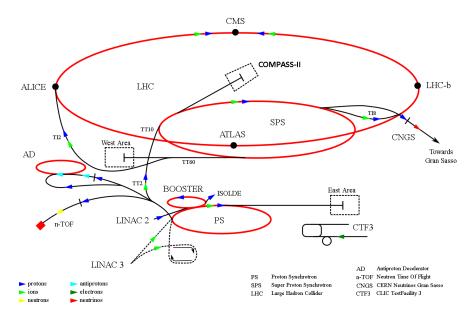

#### 3.1 Der Strahl

Das COMPASS-II Experiment ist für unterschiedliche Strahlkonfigurationen ausgelegt. So können wahlweise positive beziehungsweise negative Myonen, Pionen oder Elektronen als Strahlteilchen verwendet werden. Die Beschleunigung der benötigten Protonen erfolgt durch das SPS<sup>1</sup>, worin Protonen bis zu 450 GeV/c beschleunigt werden. Die Protonen werden dann teilweise ausgekoppelt und in Richtung COMPASS-II Experiment (siehe Abbildung 3.1) in die M2-Beamline geleitet. Dort treffen sie auf ein Beryllium-Target ("primary target T6") mit einer wählbaren Dicke von bis zu 60 cm. Diese kann je nach gewünschter sekundären Strahlintensität verändert werden.

Abbildung 3.1: Übersicht über den Beschleunigerkomplex am CERN [35].

Für die DVCS-Messung (vergleiche Abschnitt 2.5) sind polarisierte Myonen  $\mu^{\pm}$ nötig. Diese erhält man größtenteils durch den paritätsverletzenden schwachen Zerfall von geladenen Kaonen  $K^{\pm}$  und Pionen  $\pi^{\pm}$ , die nach dem Aufprall der Protonen auf das Beryllium-Target entstehen:

$$K^{+} \to \mu^{+} + \nu_{\mu}, \quad \pi^{+} \to \mu^{+} + \nu_{\mu},$$

(3.1)

$K^{-} \to \mu^{-} + \bar{\nu_{\mu}}, \quad \pi^{-} \to \mu^{-} + \bar{\nu_{\mu}}.$  (3.2)

$$K^- \to \mu^- + \bar{\nu_{\mu}}, \quad \pi^- \to \mu^- + \bar{\nu_{\mu}}.$$

(3.2)

Der Zerfallsprozess und die Impulsselektion findet in einem 600 m langen Tunnel statt, bevor der Myonstrahl auf das "eigentliche" Target beziehungsweise die Wechselwirkungszone des COMPASS-II Experiments trifft. Davor wird der Teilchentrahl durch mehrere Quadrupol- und Dipolmagnete fokusiert und so abgelenkt, das die Myonen möglichst mittig auf das Target treffen. Aufgrund der Paritätsverletzung

<sup>&</sup>lt;sup>1</sup>SPS = Super Proton Synchrotron

obiger Zerfälle sind die Myonen natürlicherweise polarisiert, wobei der Polarisationsgrad  $\chi_{\mu}$  vom Impulsverhältnis der Myon-  $(p_{\mu})$  und Hadronimpulse  $(p_{Had})$  abhängig ist.

$$\chi_{\mu} = f\left(\frac{p_{\mu}}{p_{Had}}\right) \tag{3.3}$$

Die Auskopplung der Protonen aus dem SPS erfolgt periodisch mit abwechselnden "Onspill"- und "Offspill"-Phasen, wobei die aktive Onspill-Phase, in der Teilchen am Experiment ankommen etwa 9,6 s, die inaktive Offspill-Phase circa  $4\times9,6$  s = 38,4 s dauert, sodass eine komplette Periode ungefähr  $5\times9,6$  s = 48 s beträgt. Die Dauer der Onspill-Phase ist unter anderem auch von der Anzahl der Experimente abhängig, an welche beschleunigte Protonen vom SPS verteilt werden. In der aktiven Phase kommen in etwa  $4\times10^7\,\mu/s$  am COMPASS-II Experiment an, wobei nicht alle Myonen genügend fokusiert werden können. Diese werden als sogenannte Halo-Myonen über ein Vetosystem bei der Triggererzeugung ausgeschlossen (vergleiche Abschnitt 3.4).

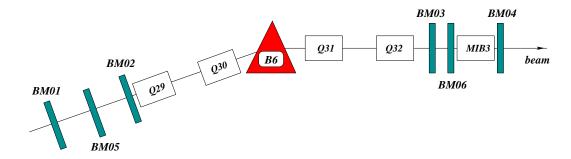

In Abbildung 3.2 ist die Strahlführung dargestellt. Die Impulse der Myonen werden mittels mehrerer BMS<sup>2</sup> (BM01 - BM06) vermessen. Die Berechnung der Myonimpulse ergibt sich aus den Krümmungsradien der Spuren, die jeweils vor und hinter den Dipolmagneten vermessen werden.

Abbildung 3.2: Führung des Teilchenstrahls in die COMPASS-Halle [34]. Um Information über den Polarisationsgrad  $\chi_{\mu}$  zu erhalten ist eine Impulsmessung der Myonen notwendig. Dies geschieht mit mehreren BMS-Hodoskopen. Die Kenntnis des Impulses ist für das Experiment wesentlich. Der Dipolmagnet B6 lenkt die Strahlteilchen in die Horizontale ab, bevor diese am Experiment ankommen.

# 3.2 Das Flüssigwasserstoff-Target

Für das DVCS-Programm wird ein sehr reines Proton-Target benötigt, um die exklusive Reaktion  $\mu p \to \mu p \gamma$  zu vermessen. Deshalb wird ein 2,5 m langes Target verwendet, welches mit flüssigem Wasserstoff ( $LH_2$ ) gefüllt ist. Das Target ist für den Nachweis rückgestoßener Protonen von einem Rückstoß-Detektor (RPD³) umgeben. Dieser wird "CAMERA⁴" genannt und in Abschnitt 3.3.2 beschrieben. Die Länge

$<sup>^{2}</sup>BMS = Beam Momentum Station$

<sup>&</sup>lt;sup>3</sup>RPD = Recoil Proton Detector beziehungsweise Rückstoß-Proton-Detektor

<sup>&</sup>lt;sup>4</sup>CAMERA = COMPASS Apparatus for Measurements of Exclusive ReActions

des Targets wurde so gewählt, dass die Luminosität des Myonstrahls, die sowohl von der Targetlänge als auch von der Strahlintensität abhängt, ungefähr  $10^{32}\,cm^{-2}s^{-1}$  beträgt.

# 3.3 Das COMPASS-II-Spektrometer

Das COMPASS-II-Spektrometer ist zweistufig aufgebaut. Es besteht aus dem LAS $^5$  zum Nachweis von Teilchen mit kleinen Impulsen und großen Streuwinkeln bis  $\pm 180\,\mathrm{mrad}$  und dem dahinter liegenden SAS $^6$ , wo höherenergetische Teilchen mit kleineren Streuwinkeln bis  $\pm 30\,\mathrm{mrad}$  nachgewiesen werden. Die beiden Teile des Experiments bestehen aus "ähnlichen" Detektorkomponenten, wobei diese jeweils Aussparungen besitzen, sodass unter kleinen Winkeln gestreute Teilchen möglichst ungehindert auf die nachfolgenden Detektoren auftreffen können. Eine detaillierte Darstellung des COMPASS-II-Spektrometers ist in Abbildung 3.3 gezeigt. Im Folgenden werden die größten unter den Detektoren am COMPASS-II Experiment kurz erläutert.

#### • LAS:

- 1. Der CAMERA-Detektor umhüllt das  $LH_2$ -Target und registriert rückgestoßene Protonen (vergleiche Abschnitt 3.3.2).

- 2. Der Dipolmagnet SM1 steht im Anschluß an das Target und lenkt die Teilchen in der horizontalen Ebene ab. Er besitzt ein Feldintegral von 1 Tm.

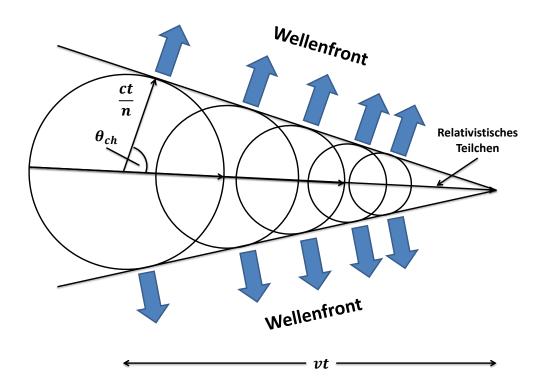

- 3. Mit dem RICH $^7$ -1 Detektor werden geladene Teilchen im kinematischen Bereich zwischen  $2,5\,\mathrm{GeV/c}$  und  $50\,\mathrm{GeV/c}$  identifiziert [38].

Dieser Detektor registriert sogenannte Cherenkov-Strahlung  $(\gamma)$ , die immer dann emmitiert wird, wenn sich ionisierende Teilchen innerhalb eines Mediums schneller als deren Phasengeschwindigkeit bewegen:

$$v > \frac{c}{n},\tag{3.4}$$

wobei c die Lichtgeschwindigkeit in Vakuum und n den Brechungsindex des Mediums bezeichnet. Dies lässt sich durch ein zeitabhängiges Dipolmoment aufgrund einer asymmetrischen Ladungsverteilung innerhalb des Mediums, hervorgerufen durch das relativistische Teilchen, erklären. Die Cherenkov-Strahlung wird senkrecht zur Polarisationsebene abgestrahlt (siehe Abbildung 3.4). Die Abhängigkeit des Abstrahlungswinkel  $\theta$  von der Geschwindigkeit  $v = \beta c$  zeigt folgende Relation:

$$\cos \theta_{ch} = \frac{1}{n\beta} = \frac{1}{n} \cdot \sqrt{\frac{1}{1 + \frac{m^2}{p^2}}}.$$

(3.5)

$<sup>^5</sup> LAS = Large Angle Spectrometer$

<sup>&</sup>lt;sup>6</sup>SAS = Small Angle Spectrometer

<sup>&</sup>lt;sup>7</sup>RICH-Detektor = Ring Imaging CHerenkov-Detektor

Abbildung 3.3: Isometrische Ansicht des COMPASS-II Experiments mit der Simulationssoftware TGEANT [36, 37].

- 4. Mit einem elektromagnetischen Kalorimeter wird die Energie der Elektronen  $e^{\pm}$  und Photonen  $\gamma$  bestimmt (ECAL0 und ECAL1 in Abbildung 3.3). Elektromagnetische Kalorimeter fungieren als Schauerzähler. Durch Wechselwirkungen hochenergetischer Photonen  $\gamma$  und Elektronen  $e^{\pm}$  werden kaskadenförmige Schauer gebildet, womit ein Nachweis bis zu einer Energie von etwa 100 MeV erfolgen kann.

- 5. Ein hadronisches Kalorimeter (HCAL1) bestimmt die Energie der Hadronen. Durch ein primäres hadronisches Teilchen kommt es durch eine Serie inelastischer hadronischer Wechselwirkungen ebenfalls zur Schauerbildung.

- 6. Der Myon-Filter MF1 schließt den ersten Teil des Experiments ab. Es wird ein 60 cm dicker Eisenabsorber verwendet. Kann man ein Teilchen sowohl vor als auch hinter einem Myon-Filter nachweisen, handelt es sich auf Grund des hohen Durchdringungsvermögens mit hoher Wahrscheinlichkeit um ein Myon. Diese wechselwirken im Vergleich zu Hadronen

nicht stark und im Vergleich zu Elektronen geht viel weniger Energie durch Bremsstrahlung verloren [39]:

$$\frac{\Delta E_{Br}^{\mu}}{\Delta E_{Br}^{e}} = \left(\frac{m_e}{m_{\mu}}\right)^2 \approx \frac{1}{40000}.$$

(3.6)

#### • SAS:

- 1. Ein weiterer Dipolmagnet (SM2), steht direkt im Anschluss an MF1. Er besitzt ein Feldintegral von 4,4 Tm.

- 2. Ein elektromagnetisches Kalorimeter (ECAL2) bestimmt die Energie der Elektronen  $e^{\pm}$  und Photonen  $\gamma$  im SAS.

- 3. Ein weiteres hadronisches Kalorimeter (HCAL2) bestimmt die Energie der Hadronen im SAS.

- 4. Der Myon-Filter MF2 schließt den zweiten Teil des Experiments ab. Er besitzt eine dicke Betonwand (2,40 m).

- 5. Dahinter ist ein zusätzlicher Myon-Filter MF3 eingebunden. Zwischen MF2 und MF3 befinden sich weitere Spurdetektoren.

Abbildung 3.4: Entstehung eines Cherenkov-Lichtkegels in einem Medium mit Brechungsindex n unter einem Winkel  $\theta_{ch}$ , hervorgerufen durch ein ionisierendes Teilchen mit Geschwindigkeit  $v = \beta c$ .

#### 3.3.1 Spurdetektoren

Zu den oben erwähnten Detektoren kommen über das gesamte COMPASS-II-Spektrometer hinweg unterschiedliche Orts- beziehungsweise Spurdetektoren zum Einsatz. An sie werden hohe Anforderungen gestellt, da eine Vermessung der Teilchentrajektorien ohne eine präzise Ortsmessung unmöglich wäre. Im Folgenden werden die wichtigsten Spurdetektoren am COMPASS-II Experiment kurz erläutert.

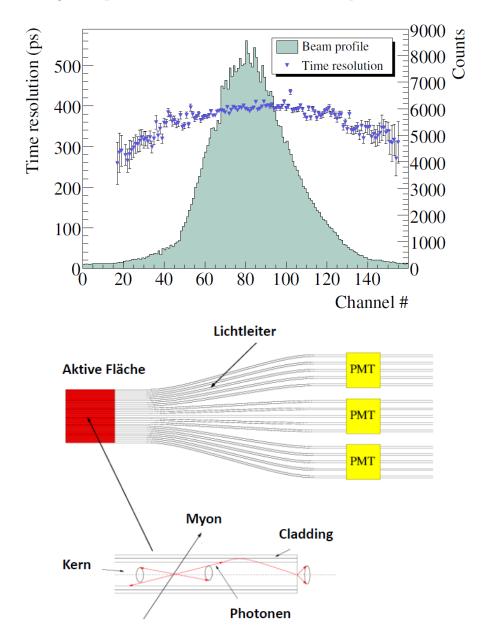

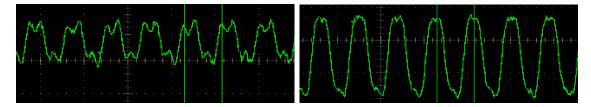

Abbildung 3.5: Zeitauflösung einer SciFi-Ebene zusammen mit dem Strahlprofil [34] (oben). Unten ist der Aufbau eines SciFi-Hodoskops abgebildet [40]. Durch ein ionisierendes Teilchen wird Szintillatorlicht erzeugt welches durch Totalreflektion an der Grenzfläche zur äußeren Hülle (Cladding) zu den Photomultipliern (PMT) befördert wird, wo es nachgewiesen werden kann.

Für die Messung des Strahls bis 3 cm um die Strahlachse kommen Detektoren zum Einsatz, die eine geringe Totzeit haben, da die Rate der Teilchen teilweise sehr hoch

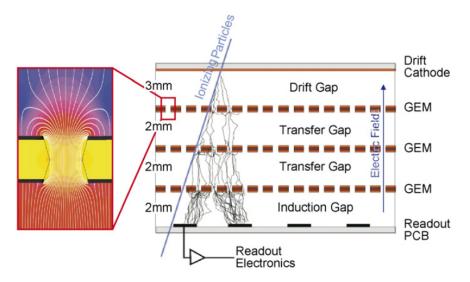

(im Bereich MHz) sein kann. Dafür eignen sich sowohl SciFis<sup>8</sup> als auch Silizium-Streifendetektoren. Aufgrund ihrer sehr guten Zeit- und Ortsauflösung ( $\approx 400\,\mathrm{ps}$ ,  $\approx 150\,\mu\mathrm{m}$  [34]) werden SciFis vor allem zur Bestimmung des Impulses der Strahlteilchen herangezogen (siehe Abbildung 3.5 oben). Diese sind dünne Fasern aus Plastikszintillator, umgeben von einem Materialmantel mit kleinerem Brechungsindex, wodurch ein ionisierendes Teilchen über Totalreflexion nachgewiesen werden kann (siehe Abbildung 3.5 unten). Silizium-Streifendetektoren werden aufgrund ihrer guten Ortsauflösung ( $\approx 10\,\mu\mathrm{m}$ ) für die Rekonstruktion der Trajektorien gestreuter Myonen beziehungsweise Strahlteilchen verwendet. Für Entfernungen zur Strahlachse im Bereich weniger cm bis etwa 50 cm werden hauptsächlich MicroMegas<sup>9</sup> und GEMs<sup>10</sup> verwendet. GEMs bestehen aus dünnen, durchlöcherten, metallbeschichteten Polymerfolien mit Lochabstand  $\approx 140\,\mu\mathrm{m}$  und Lochdurchmesser  $\approx 70\,\mu\mathrm{m}$ . Durch die Verwendung mehrerer Lagen solcher Schichten wird eine hohe Gasverstärkung erzielt (siehe Abbildung 3.6). Diese Detektoren zeichnen sich unter anderem auch durch ihre geringe Totzeit aus.

Abbildung 3.6: Die Gasverstärkung der GEMs wird lawinenartig durch mehrere Schichten erzeugt. Diese findet innerhalb der Löcher statt. Links sind die elektrischen Feldlinien schematisch dargestellt [34].

Für große Ablenkungswinkel, also weite Entfernungen zur Strahlachse kommen sehr großflächige Detektoren zum Einsatz. Darunter befinden sich Straws, DCs<sup>11</sup> und MWPCs<sup>12</sup>, deren aktive Flächen im Bereich einiger m<sup>2</sup> liegen.

#### 3.3.2 Der CAMERA-Detektor

Für das DVCS-Programm wurde der CAMERA-Detektor gebaut, der im Herbst 2012 in das Experiment eingebunden wurde. Dabei handelt es sich um einen Detektor für den Nachweis rückgestoßener Protonen, womit exklusive DVCS-Ereignisse

<sup>&</sup>lt;sup>8</sup>SciFi = Szintillierende Fasern

<sup>&</sup>lt;sup>9</sup>MicroMega = MICROMEsh GASeous structure

$<sup>^{10}</sup>$ GEM = Gas Electron Multiplier

$<sup>^{11}</sup>DC = Drift Chamber$

<sup>&</sup>lt;sup>12</sup>MWPC = Multi Wire Proportional Chamber

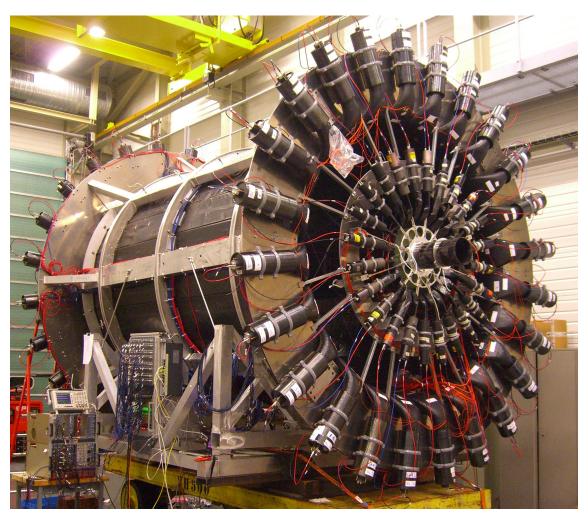

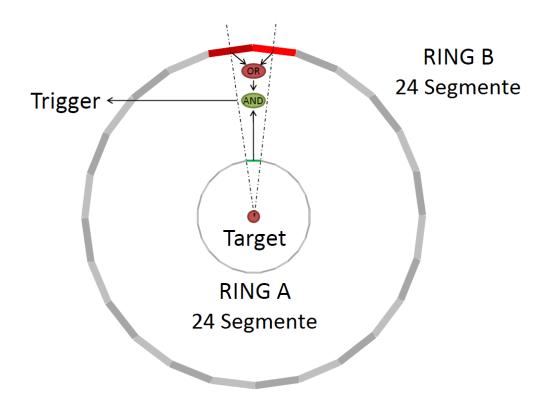

präzise detektiert werden können. Der Detektor besteht aus Szintillatorstreifen, welche an beiden Enden von PMTs ausgelesen werden. Die Szintillatorstreifen bilden zwei konzentrische Ringe – Ring A und Ring B – um das LH<sub>2</sub>-Target (siehe Abbildung 3.8). Beim Durchflug eines Teilchens durch gegenüberliegende Streifen können Trigger erzeugt werden [41]. Jeder der Ringe enthält 24 Szintillatorstreifen, sodass jeweils 15° des Raumwinkels abdeckt werden. Die Ringe sind um die Hälfte (7,5°) gegeneinander rotiert, womit die Winkelauflösung verdoppelt wird. Die Dicke der Streifen wurde so gewählt, dass gute Messungen zur Energiedeposition und Flugzeitmessungen der Protonen duchgeführt werden können, woraus der Protonimpuls bestimmt werden kann. Dazu ist eine sehr gute Zeitauflösung essentiell. In Abbildung 3.7 beziehungsweise 3.8 befinden sich Darstellungen des CAMERA-Detektors.

Abbildung 3.7: Darstellung des 4 m langen CAMERA-Detektors nach dem Zusammenbau und gegen Ende der Testphase. Die Szintillatoren die den A-Ring bilden haben die Abmessungen  $275 \times 6, 3 \times 0, 4 \, \mathrm{cm}^3$  und befinden sich  $24 \, \mathrm{cm}$  vom Mittelpunkt des Targets entfernt. Der B-Ring misst  $360 \times 30 \times 5 \, \mathrm{cm}^3$  und ist etwa  $110 \, \mathrm{cm}$  vom Mittelpunkt des Targets entfernt.

Abbildung 3.8: Schematische Darstellung der zwei Szintillatorringe und der Triggerlogik durch Koinzidenzen gegenüberliegender Streifen [20].

## 3.4 Das COMPASS-II-Trigger-System

Aufgrund der hohen Ereignisraten am COMPASS-II Experiment ist es unmöglich, alle Daten aufzunehmen. Dies ist auch nicht erstrebenswert, da nur die physikalisch interessanten Ereignisse aufgezeichnet werden sollen. Die Entscheidungen dafür übernimmt ein Triggersystem, welches Ereignisse herausselektiert und uninteressante verwirft. Für eine Triggerentscheidung benötigt das System in etwa 1,922  $\mu$ s. Dies ist die Zeit zwischen Durchflug eines Myons durch den Detektor FI01<sup>13</sup> und der Generierung eines Triggers [42]. Das Trigger-Signal initialisiert den Auslesevorgang der Daten. Diese liegen auf den Front-End-Karten bereit, die direkt an den Detektoren angebracht sind. Eine schnelle Triggerentscheidung zu treffen ist gerade deshalb essentiell, da die Auslesemodule über begrenzten Speicherplatz zum zwischenspeichern der Daten verfügen.

### 3.4.1 Der Myontrigger

Myontrigger werden durch Vermessung der Spur eines gestreuten Myons erzeugt. Die Entscheidung wird sowohl mit Hilfe mehrerer Triggerhodoskope, als auch mit einer Messung des Energieverlusts durch Kalorimeter getroffen. Dabei werden gestreute Myonen von Halo-Myonen getrennt. Dies wird unter anderem durch ein vor dem Target installiertes Veto-Triggersystem erreicht. Wird ein Halo-Myon detektiert, so wird für eine gewisse Zeit das Auslösen eines Triggers verhindert.

<sup>&</sup>lt;sup>13</sup>Hierbei handelt es sich um szintillierende Fasern vor dem Targetbereich.

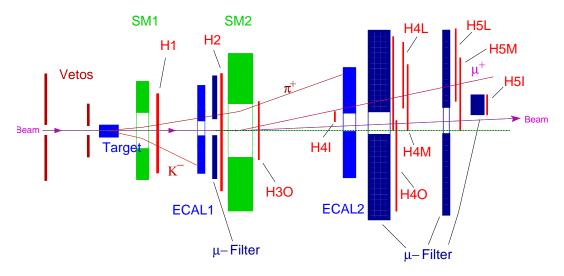

Eine schematische Darstellung des Triggersystems befindet sich in Abbildung 3.9, dabei sind H4I, H5I die inneren, H4M, H5M die mittleren und H3O, H4O die äußeren Triggersysteme, die jeweils aus zwei Szintillator-Hodoskopen bestehen. Außerdem existiert noch ein sogenanntes Leitertriggersystem H4L, H5L.

Durch die vier Triggersysteme ist es möglich, Myonen in einem großen kinematischen Bereich zu detektieren. Myonen mit geringem relativen Energieverlust

$$0, 2 < \frac{\Delta E}{E_0} < 0, 5$$

werden vom inneren Triggersystem erfasst. Im Bereich

$$0.5 < \frac{\Delta E}{E_0} < 0.9$$

werden diese vom Leitertriggersystem registriert. Dafür muss jeweils der Ablenkungswinkel durch den Magneten gemessen werden. Mit einer geforderten unteren Schranke der Energiedeposition im hadronischen Kalorimeter werden Hintergrundereignisse ausgeschloßen.

Für Ereignisse mit  $Q^2 > 0, 5 (GeV/c)^2$  ist der Streuwinkel des Myons groß genug um vom äußeren Triggersystem mit der sogenannten Vertical-Target-Pointing-Methode erfasst zu werden. Diese wird ausführlich in [43] beschrieben.

Abbildung 3.9: Darstellung der Triggerhodoskope im COMPASS-II-Spektrometer [29].

### 3.4.2 Der Protontrigger

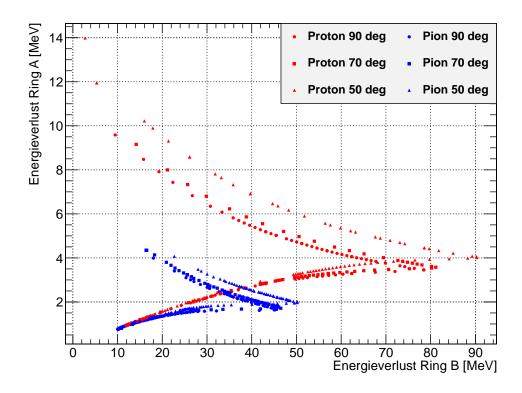

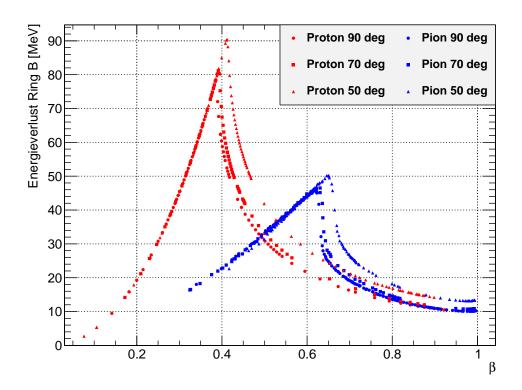

Entscheidungen für Protontrigger werden durch den CAMERA-Detektor getroffen [41]. Die Triggergenerierung erfolgt durch eine Koinzidenzmessung, sobald ein Proton in zwei sich gegenüberliegenden Szintillatoren (Ring A und Ring B) detektiert wird (vergleiche Abbildung 3.8). Dabei ist es wichtig, Protonen zweifelsfrei zu identifizieren, um sie von anderen Teilchen wie Pionen oder  $\delta$ -Elektronen auseinanderzuhalten. Dafür wird eine Messung der Flugzeit und des Energieverlusts sowohl für Ring A als auch für Ring B herangezogen, womit eine Separation in bestimmten kinematischen Bereichen möglich ist (vergleiche Abbildung 3.10).

Abbildung 3.10: Simulation mit TGEANT [36, 37]: Auftragung der Energiedeposition in Ring A für Protonen (rot) und Pionen (blau) gegen die Energiedeposition in Ring B (oben). Unten ist der Energieverlust in Ring B in Abhängigkeit von der Teilchengeschwindigkeit  $\beta = v/c$  aufgetragen.

#### 3.5 Die Datennahme

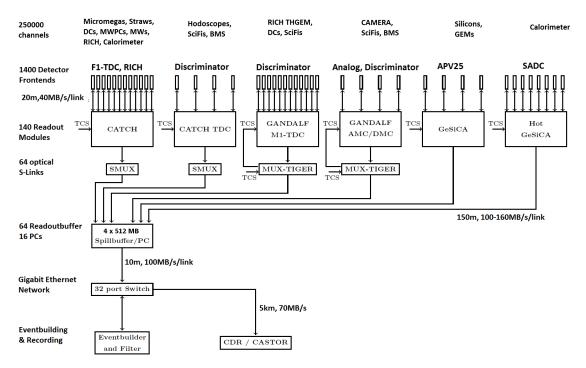

Das Datennahmesystem (DAQ<sup>14</sup>) am COMPASS-II Experiment muss in der Lage sein, Datenraten bis zu mehreren Gigabyte pro Sekunde zu verarbeiten. Diese Datenrate kommt durch die große Anzahl an Detektorkanälen (etwa 250000), die teilweise sehr hohen Triggerraten (bis zu 100 kHz) und durch die große Hitrate (im Bereich MHz) in einzelnen Kanälen zustande. Eine Zusammenfassung der Datenweiterleitung von den Detektorsignalen bis zur Speicherung auf Magnetbändern über die zentrale Datenannahme des CERN ist in Abbildung 3.11 dargestellt.

Die Detektorsignale werden vor Ort mittels ADCs<sup>15</sup> oder TDCs<sup>16</sup> auf den Front-End-Karten digitalisiert und in Buffern zwischengespeichert. ADCs tasten die Amplitude des Signals ab und digitalisieren diese. Ein TDC ermittelt den Zeitpunkt einer Zustandsänderung auf einem digitalen Signal und gibt die Zeitmarke in digitaler Form aus. Viele der am COMPASS-II Experiment zum Einsatz kommenden Front-End-Karten und Module, wie das GANDALF- und das CATCH<sup>17</sup>-Modul wurden in Freiburg entwickelt. Dabei wurde auf eine möglichst flexible Nutzbarkeit geachtet. So lassen sich auf dem CATCH-Modul unterschiedliche Front-End-Karten wie beispielsweise Scaler-CMCs<sup>18</sup> oder TDC-CMCs anbringen. Das GANDALF-Modul verfügt über ähnliche und weitere Möglichkeiten. Eine ausführlichere Beschreibung des GANDALF-Moduls befindet sich in Kapitel 4. Es besteht die Möglichkeit, bis zu 18 GANDALF-Module zentral über einen VXS-Switch auszulesen (siehe Kapitel 4). Diese Aufgabe übernimmt das Freiburger TIGER<sup>19</sup>-Modul [44]. Desweiteren kommen für die Auslese der Silicon- und GEM-Detektoren die in München entwickelten GeSiCA<sup>20</sup>-Module zum Einsatz.

Die Steuerung der Datenauslese übernimmt das Trigger Control System (TCS) [45], welches Trigger über optische Fasern an alle Auslesemodule verteilt. Für eine nachträgliche Zuordnung der Datanpakete zu den Triggern werden noch weitere Informationen zu den Triggern versendet (siehe Abschnitt 4.5). Die Daten der Auslesemodule werden über Glasfasern mit bis zu 160 MByte/s zu den Readout Buffer-PCs (ROBs) weitergeleitet. Von dort aus erfolgt eine Weiterleitung an Eventbuilder-PCs, die vollständige Events generieren, indem die Daten aller Detektoren zu einem bestimmten Event zusammengefasst werden. Anschließend erfolgt die Weiterleitung der Daten an einen zentralen Datenspeicher (CDR<sup>21</sup>) des CERN, zur Speicherung auf Festplatten und später auf Magnetbändern.

<sup>&</sup>lt;sup>14</sup>DAQ = Data Acquisition System

$<sup>^{15}</sup>ADC = Analog-to-Digital-Converter$

$<sup>^{16}</sup>$ TDC = Time-to-Digital-Converter

$<sup>^{17}</sup>$ CATCH = COMPASS Accumulate Transfer and Control Hardware

<sup>&</sup>lt;sup>18</sup>CMC = Common Mezzanine Card, Aufsteckkarte für das CATCH-Modul

<sup>&</sup>lt;sup>19</sup>TIGER = Trigger Implementation for GANDALF Electronic Readout

<sup>&</sup>lt;sup>20</sup>GeSiCA = GEM and Silicon Control and Acquisition

<sup>&</sup>lt;sup>21</sup>CDR = Central Data Recording

Abbildung 3.11: Darstellung des Datennahmesystems am COMPASS-II Experiment [46].

# 4. Das GANDALF Framework

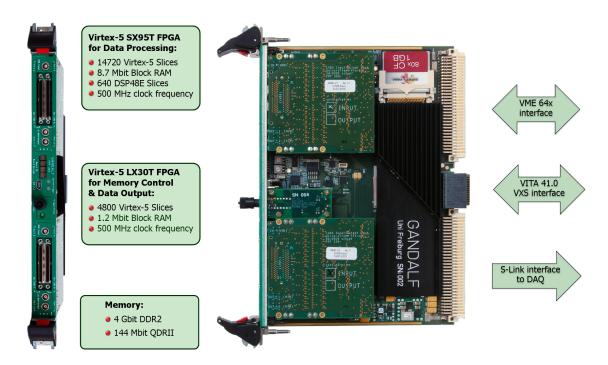

Wie im vorangehenden Kapitel erläutert, werden für die Auslese und Verarbeitung der Detektorsignale zum Teil sehr hohe Anforderungen an die Elektronik gestellt. Zur Auslese der szintillierenden Fasern wird das in Freiburg entwickelte GANDALF-Modul zum Einsatz kommen. Dies ist ein VXS/VME64x-Modul, welches zur Echtzeitanalyse und Digitalisierung hochfrequenter Signale geeignet ist und die CATCH-Module zukünftig vermehrt ersetzen wird. Bei der Entwicklung des GANDALF-Moduls wurde großen Wert auf vielseitige Anwendungsmöglichkeiten gelegt. So können je nach Einsatzzweck verschiedene Aufsteckkarten (Mezzanine Cards) angebracht werden. Dieses Prinzip hat sich schon bei den CATCH-Modulen bewährt, die bei COMPASS seit Jahren erfolgreich eingesetzt werden. Das Herzstück des GANDALF-Moduls ist ein Xilinx Virtex-5 FPGA, der sich auf der Hauptplatine (Mainboard) befindet. Dieser verfügt über sehr leistungsstarke Logikeinheiten. Außerdem ist das Mainboard mit viel Speicher ausgestattet, der als Puffer für große Datenmengen verwendet werden kann. Das GANDALF-Modul kam ursprünglich als Transientenrekorder für die Auslese eines Rückstoß-Proton-Detektors zum Einsatz [20, 47, 48]. Außerdem konnten bereits weitere Funktionen wie beispielsweise ein 128-Kanal-TDC [49] beziehungsweise ein 64-Kanal-Meantimer [50] implementiert werden. Der im Rahmen dieser Diplomarbeit entwickelte FPGA-basierte Scaler und dessen Vereinigung mit dem TDC auf einem einzigen GANDALF-Modul wird in den Kapiteln 5 und 6 beschrieben.

#### 4.1 Das GANDALF Mainboard

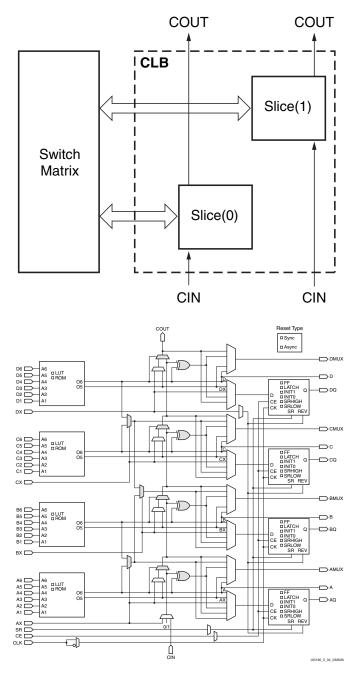

Das GANDALF Mainboard ist ein 6U VME64x/VXS Modul (233x160mm² [51]), welches über zwei Steckplätze für digitale oder analoge Aufsteckkarten verfügt. Diese dienen als Verbindung der Detektorsignale mit einem Xilinx Virtex-5 FPGA (Modell: XC5VSX95T [13]), im Folgenden DSP¹-FPGA genannt. Dieser verfügt über 58880 Flipflops auf insgesamt 58800/4 = 14720 Virtex-5-Slices und mit 8 Mbit BlockRAM über genügend Speicher um auch anspruchsvolle Logiken und Funktionen implementieren zu können. Diese können mit einer maximalen Frequenz von bis zu 500 MHz getaktet werden (CLK500MHz). Unter anderem kann für die effiziente Implementierung bestimmter Operationen auf 640 sogenannte DSP-Slices zurückgegriffen werden. Diese werden bei der Entwicklung des Scalers (siehe Kapitel 5) unter anderem für Additionen verwendet.

Die Hauptplatine verfügt über einen weiteren FPGA (Modell: XC5VLX30T [13]), im Folgenden MEM-FPGA genannt. Dieser dient als Schnittstelle zum Hauptspeicher, welcher sich hauptsächlich aus dem 144 Mbit QDRII+² Speicher und dem 4 Gbit DDR2³ Speicher zusammensetzt. Dieser findet beispielsweise in der Zwischenspeicherung von Daten Verwendung, bevor die Übermittlung an das zentrale Datennahmesystem erfolgt. Der QDRII+ Speicher kann aufgrund unabhängiger Ports für Lese- und Schreibzugriffe jeweils gleichzeitig mit bis zu 14,4 Gbit/s beschrieben beziehungweise ausgelesen werden, wohingegen der DDR2 Speicher mit bis zu 4 Gbit/s beschrieben oder ausgelesen werden kann. Die Kommunikation des DSP- und des MEM-FPGA erfolgt über eine serielle Hochgeschwindigkeits-Schnittstelle, basierend auf dem Aurora Protokoll [52]. Über sogenannte "Rocket IO GTP Transceiver"-Elemente [53] ist über insgesamt acht differentielle Leitungen eine maximale Datenübertragungsrate von bis zu 25 Gbit/s möglich.

Das GANDALF-Modul verfügt außerdem über einen Xilinx Cool-Runner CPLD<sup>4</sup>, welcher zur Konfiguration des DSP- beziehungsweise des MEM-FPGAs über die VME-CPU dient. Somit lassen sich die FPGAs auch während des Experiments zum Beispiel über einen Konfigurationsspeicher (Config-Mem), der mit dem CPLD verbunden ist, von außen konfigurieren (siehe Abschnitt 4.6). Der Vorteil eines CPLDs besteht unter anderem darin, dass er nach dem Einschalten des Moduls nicht erneut programmiert werden muss, während man FPGAs jedes mal mit einer sogenannten "Bitstream"-Datei initialisieren muss. Die Programmierung der FPGAs erfolgt in der Regel über den VME-Bus, jedoch ist dies auch mit dem "SystemACE"-Tool über eine CompactFlash-Karte auf der Hauptplatine möglich [54].

Für den Empfang der TCS-Signale kommt außerdem eine weitere Aufsteckkarte zum Einsatz. Diese wird in Abschnitt 4.4.1 beschrieben. Eine Darstellung des GANDALF-Moduls befindet sich in Abbildung 4.1.

$<sup>^{1}\</sup>mathrm{DSP}=\mathrm{Digital\ Signal\ Processing}$

$<sup>^{2}</sup>QDR = Quad Data Rate$

$<sup>^{3}</sup>DDR = Double Data Rate$

<sup>&</sup>lt;sup>4</sup>CPLD = Complex Programmable Logic Device

Abbildung 4.1: Abbildung des GANDALF-Moduls mit zwei digitalen 64-Kanal-Aufsteckkarten (Input). In der Mitte ist die Takt/Trigger-Interface-Karte (Gimli-Karte) zu sehen. Außerdem sind die wichtigsten Schnittstellen und die Spezifikationen der auf dem GANDALF-Modul zum Einsatz kommenden FPGAs sowie des Hauptspeichers angegeben [49].

#### 4.2 Schnittstellen des GANDALF-Moduls

#### 4.2.1 VME64x

Das GANDALF-Modul (VME-Slave) wird über zwei 160-polige Anschlüsse (P1, P2) mit der Backplane des VME<sup>5</sup>-Crates verbunden (siehe Abbildung 4.1 rechts). Dies ermöglicht eine Konfiguration aller GANDALF-Module im Crate über eine Linux-basierte VME-CPU (VME-Master), welche im gleichen Crate stecken muss. Dabei werden die VME64x-Spezifikationen erfüllt, welche in [51] definiert sind. Über den VME-BUS, der sich aus je einem 32 Bit breiten Adress- und Datenbus zusammensetzt, ist eine Übertragungsrate von bis zu 40 MByte/s möglich. Über die VME64x-Schnittstelle können interne Parameter mit einfachen Befehlen abgefragt respektive verändert werden. Somit kann beispielsweise eine Überwachung aller GANDALF-Module im VME-Crate durch Abfrage der Temperatur auf dem Mainboard erfolgen.

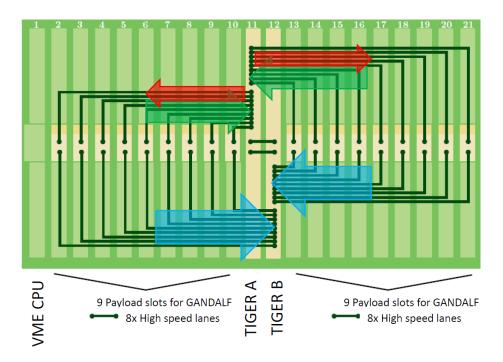

#### 4.2.2 VXS

Es besteht die Möglichkeit, Daten von bis zu 18 GANDALF-Modulen im VME-Crate zentral über ein TIGER-Modul zu übertragen [44]. Die dafür benutzte VXS-Schnittstelle befindet sich zwischen P1 und P2 (siehe Abbildung 4.1). Die Kommunikation erfolgt über acht unidirektionale Hochgeschwindigkeitsleitungen (sie-

<sup>&</sup>lt;sup>5</sup>VME = VERSA Module Eurocard

he Abbildung 4.2). VXS ist ein ANSI<sup>6</sup>-Standard und wird in [55] definiert. Dieser stellt eine Erweiterung des VME64x-Standards dar. Die Datenübermittlung erfolgt über optische Fasern. Dazu wird an der Rückseite der VME-Backplane eine SLink-Interfacekarte angebracht [56]. Diese erlaubt eine Datenübertragungsrate von bis zu 160 MByte/s. Die Datenübertragung an die DAQ der in diesem Projekt entwickelten GANDALF-Firmware findet am COMPASS-II Experiment über einen "Readout"-TIGER [44] statt.

Abbildung 4.2: Schematische Darstellung der VXS-Backplane: Der erste Slot ist für die VME-CPU bestimmt, welche keine VXS-Verbindung hat. GANDALF-Module können auf den Positionen 2 bis 10 und 13 bis 21 platziert werden. Für TIGER-Module sind die Positionen 11 und 12 vorgesehen. Über zwei Leitungen werden TCS-Signale (Takt- und Datensignal) an die GANDALF-Module übertragen (rot, TIGER A). Die Auslese der GANDALF-TCS-Daten findet über vier Leitungen statt (grün, TIGER A). Für die Übertragung von ungetriggerten Hit-Informationen sind acht Leitungen vorgesehen. Dieser Datenstrom wird von TIGER B empfangen (blau) [57].

#### 4.2.3 Takt- & Trigger-Schnittstelle

Für die Übertragung der Signale vom TCS auf den DSP-FPGA besitzt das GANDALF-Modul eine weitere Schnittstelle für die sogenannte "Gimli-Karte" (siehe Abschnitt 4.4.1), womit sowohl ein sehr präzises 155, 52 MHz-Taktsignal als auch Trigger und deren zugehörige Informationen übertragen werden (siehe Abschnitt 4.5). Ein einheitliches Taktsignal ist vor allem für das synchrone Schalten bei der Verwendung mehrerer GANDALF-Module essentiell.

$<sup>^6 \</sup>mathrm{ANSI} = \mathrm{American}$  National Standards Institute

4.3. Taktsignale 35

# 4.3 Taktsignale

Neben dem 155, 52 MHz-Taktsignal besteht auf dem GANDALF-Modul die Möglichkeit nach Bedarf weitere jitterarme Taktsignale zu erzeugen. Diese können aus dem TCS-Signal mit einem sogenannten Clock Multiplier Chip (Si5326) von Silicon Labs [58] erzeugt und über zwei Signalausgänge auf den beiden FPGAs bereitgestellt werden. Dabei können Frequenzen  $\nu_{Si}$  zwischen 2 kHz bis maximal 945 MHz

$$\nu_{Si} = \nu_{TCS} \cdot \frac{n_1}{n_2},\tag{4.1}$$

für natürliche Zahlen  $n_1$ ,  $n_2$  generiert werden. Auf diesem Weg wird das in Abschnitt 4.1 erwähnte Signal CLK500MHz erzeugt.

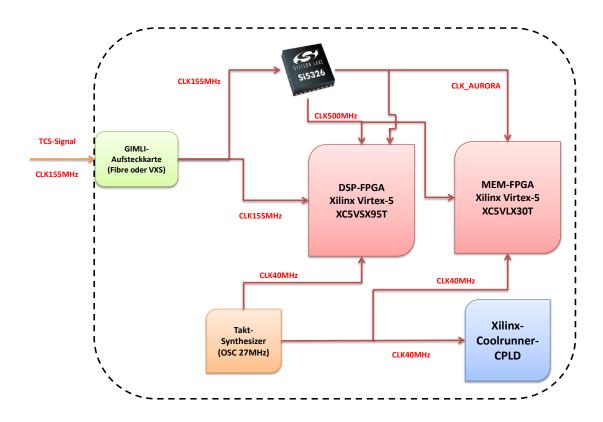

Desweiteren befindet sich ein programmierbarer Takt-Synthesizer CDCE949 [59] auf der Hauptplatine, der über einen Oszillator einen 27 MHz-Referenztakt erhält und ein 40 MHz-Taktsignal (*CLK40MHz*) generiert, welches an DSP- und MEM-FPGA sowie an den CPLD weitergeleitet wird. Eine schematische Übersicht der wichtigsten Taktsignale auf dem GANDALF-Modul zeigt Abbildung 4.3. Zusätzlich ist auf dem GANDALF-Modul ein Schwingquarz vorhanden, der mit dem CPLD verbunden ist und ein 40 MHz Taktsignal unabhängig vom TCS bereitstellt. Dieses Signal wurde in Abbildung 4.3 der Übersicht halber weggelassen.

Abbildung 4.3: Schematische Darstellung der Taktverteilung und Erzeugung der wichtigsten Taktsignale auf dem GANDALF-Modul.

#### 4.4 Aufsteckkarten

#### 4.4.1 Die Gimli-Karte

Wie in Abschnitt 4.2.3 angedeutet, wird auf den Auslesemodulen ein vom TCS erzeugtes optisches Signal entgegengenommen, welches über Glasfasern verteilt wird. Dieses Signal enthält das 155,52 MHz-Referenztaktsignal, das Triggersignal, sowie wichtige Informationen zu den Triggern wie beispielsweise Eventnummer, Spillnummer und Art des Events. Die Umwandlung des optischen in ein elektrisches Signal erfolgt auf einer Fibre-Gimli-Karte (siehe Abbildung 4.4). Diese enthält einen CLC016-Chip [60], welcher den Referenztakt aus dem seriellen Datenstrom wiederherstellt. Es besteht außerdem die Möglichkeit, das TCS-Signal über die Backplane entgegenzunehmen. Die Übertragung an die GANDALF-Module über den VXS-Bus übernimmt ein TIGER-Modul [44] (vergleiche Abbildung 4.2, roter Pfeil). Dazu ist eine VXS-Gimli-Karte nötig, die das TCS-Signal über den FPGA entgegennimmt, um es von dort aus wieder zurückzuleiten. Damit kann das Signal über die gleichen Pins am FPGA empfangen werden. Die Entgegennahme der TCS-Signale in diesem Projekt findet über ein TIGER-Modul (Gimli-Typ VXS) statt.

Abbildung 4.4: Bild einer Fibre-Gimli (links) und einer VXS-Gimli (rechts) [57].

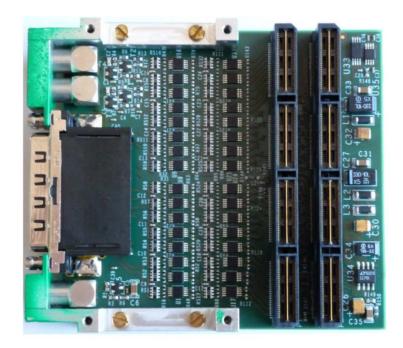

# 4.4.2 Die digitale Mezzanine-Card

Neben der Möglichkeit, zwei AMCs<sup>7</sup> anzubringen, welche verwendet werden können um insgesamt 16 analoge Eingangssignale pro GANDALF-Modul zu digitalisieren, können auch digitale Mezzanine-Cards (DMC) aufgesteckt werden. Für die Entwicklung der Firmware zur Auslese der szintillierenden Fasern werden DMCs benötigt, die das Detektorsignal für die Signalverarbeitung zum DSP-FPGA weiterleiten. Das GANDALF-Modul erlaubt das Anbringen zweier DMCs mit jeweils 64 differentiellen Eingangssignalen (LVDS oder LVPECL<sup>8</sup>), die über differentielle Buffer mit dem DSP-FPGA verbunden werden. Somit können mit einem GANDALF-Modul maximal 128 Detektorkanäle verarbeitet werden.

Die Anbindung an das Eingangssignal erfolgt mit jeweils zwei differentiellen 32-Kanal VHDCI-Steckern [61] pro DMC. Die Signale werden von NB4N855S Clockbeziehungsweise Datenbuffern gepuffert, die laut Datenblatt [62] mit maximal 1 ps einen sehr kleinen RMS-Jitter aufweisen. Außerdem garantiert der Hersteller Eingangsfrequenzen bis 1 GHz verarbeiten zu können. Jede DMC besitzt zwei NIM-Ausgänge und einen NIM-Eingang, welche sich neben den VHDCI-Steckverbindungen befinden (siehe Abbildung 4.5). Diese können über LEMO-Verbindungen externe Signale zum DSP-FPGA beziehungsweise interne Signale nach außen weiterleiten.

$<sup>^{7}</sup>$ AMC = Analog Mezzanine-Card

<sup>&</sup>lt;sup>8</sup>LVPECL = Low Voltage Positive Emitter Coupled Logic

Abbildung 4.5: Das Bild zeigt eine DMC (links), die über zwei VHDCI-Stecker die Signale von insgesamt 64 Detektorkanälen entgegennehmen beziehungsweise im "Output-Modus" diese nach außen weiterleiten kann. Rechts sind die VHDCI-Anschlüsse und der NIM-Eingang beziehungsweise die zwei NIM-Ausgänge von vorne zu sehen [49].

Es besteht außerdem die Möglichkeit durch gedrehte Montage der Signalbuffer die DMC als 64-Kanal Output-Karte zu produzieren. Diese werden zum Beispiel zum Testen verwendet, indem ein "Output-GANDALF" Testsignale erzeugt und über LVDS-Kabel an einen "Input-GANDALF" sendet, der die zu testende Logik enthält. Somit kann die Einbindung in das Experiment unter Laborbedingungen simuliert werden (siehe Kapitel 7).

# 4.5 Das TCS Interface

Das Trigger Control System am COMPASS-II Experiment besteht aus zwei Komponenten. Ob ein "interessantes" Event stattgefunden hat, wird anhand einer Triggerlogik entschieden, welche mit einer dieser beiden Komponenten (TCS-Controller) verbunden ist [45]. Wird eine Triggerentscheidung getroffen, so generiert der TCS-Controller charakteristische Markierungen zu dem Event, welche an alle Auslesemodule verteilt werden und mit in die Daten geschrieben werden. Bei der Triggergenerierung wird eine minimale Totzeit von  $0,4\,\mu$ s eingehalten, sodass für diese Zeit nach einem Trigger kein zweiter kommen darf. Eine Zusammenfassung der vom TCS-Controller generierten Triggerinformationen befindet sich in Tabelle 4.1.

Die zweite Komponente ist ein TTCex-Modul [63], welches dazu verwendet wird, die Triggerinformation in einen seriellen Datenstrom zu kodieren und in ein optisches Signal zu konvertieren, welches synchron über Glasfasernleitungen an alle

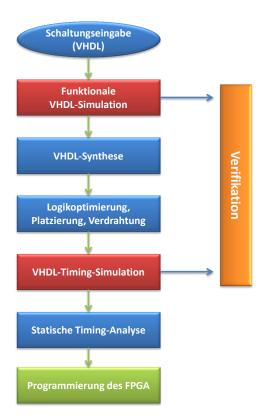

Auslesemodule des Experiments verteilt wird. Diese können beispielsweise von einer Fibre-Gimli in elektrische Signale umgewandelt und auf den FPGAs bereitgestellt werden. Das TCS Interface stellt eine VHDL-Komponente dar und wird auf dem DSP-FPGA implementiert. Dort wird der Datenstrom mit einem Seriell-zu-Parallel-Wandler dekodiert.

Tabelle 4.1: Beschreibung der Triggerinformationen, die vom TCS-Controller erzeugt werden. Die Breite der Signalbusse ist in Klammern () angegeben [64].

| Information      | Beschreibung                                                                                                                                                                                                                                                                                                                |  |  |  |

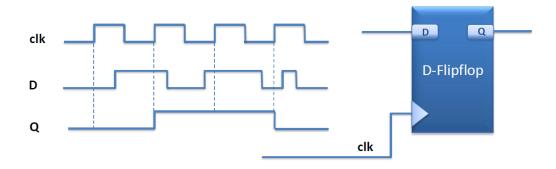

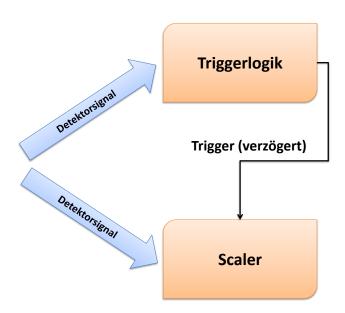

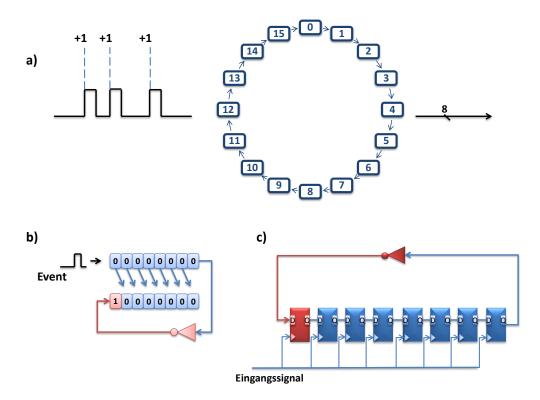

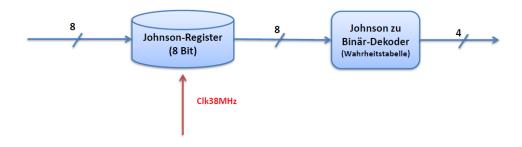

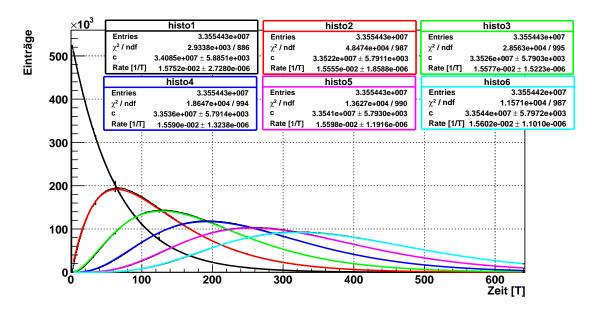

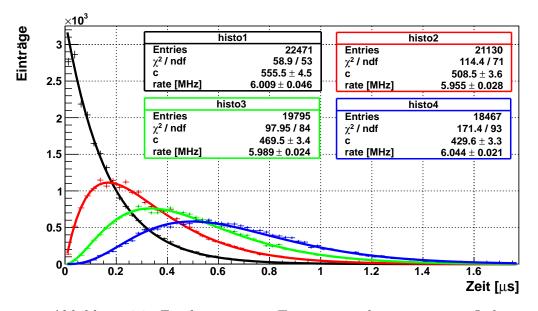

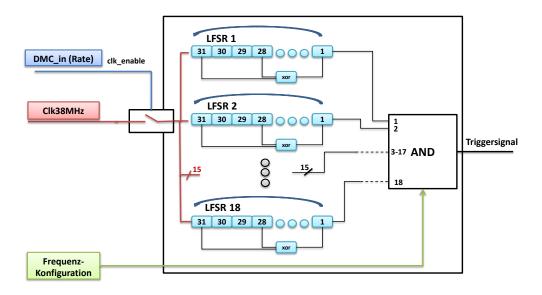

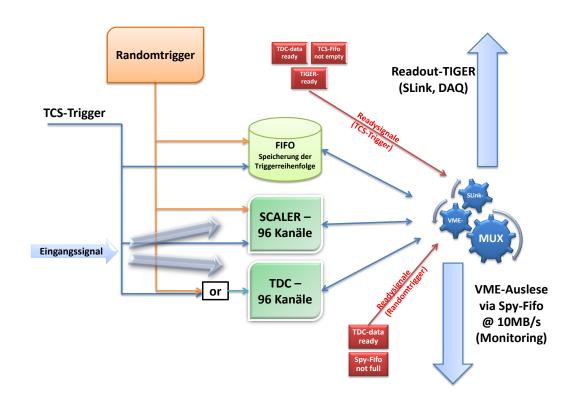

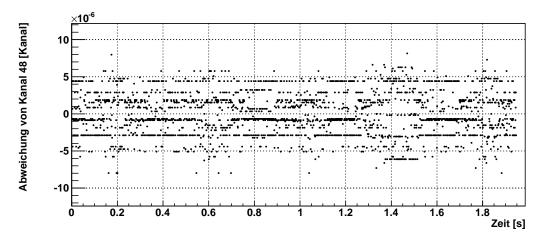

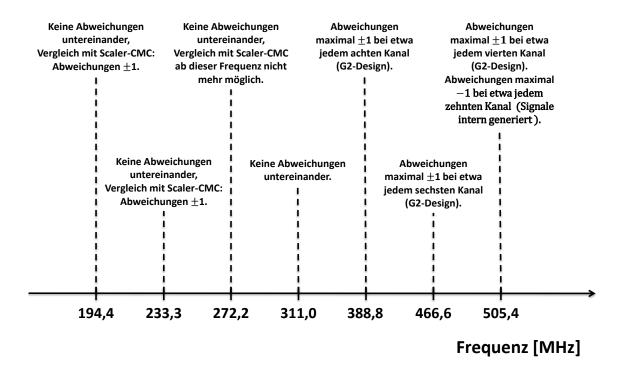

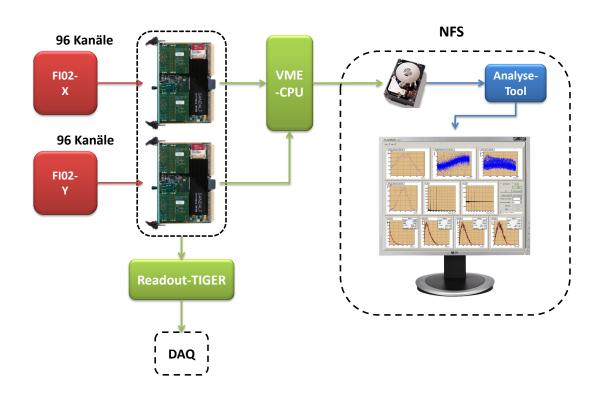

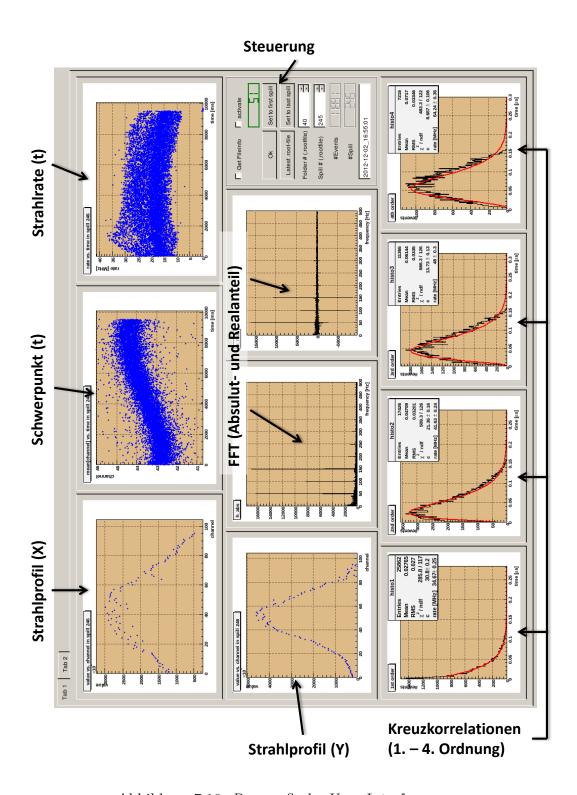

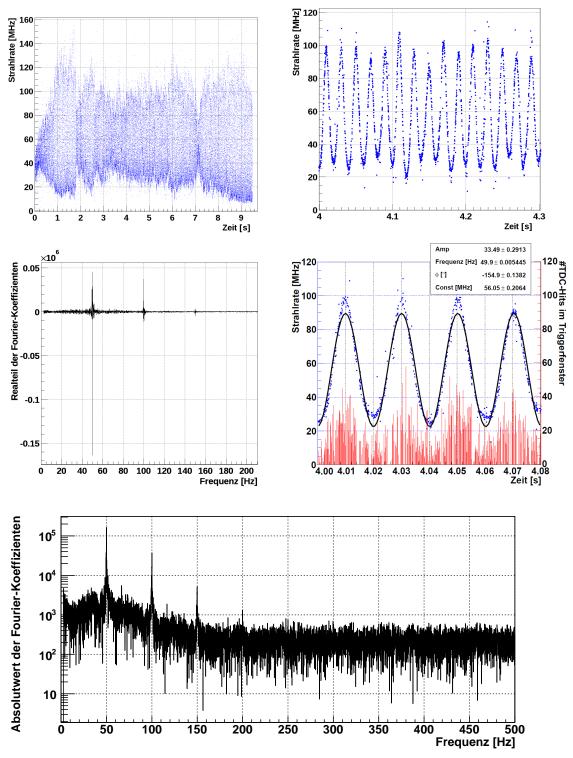

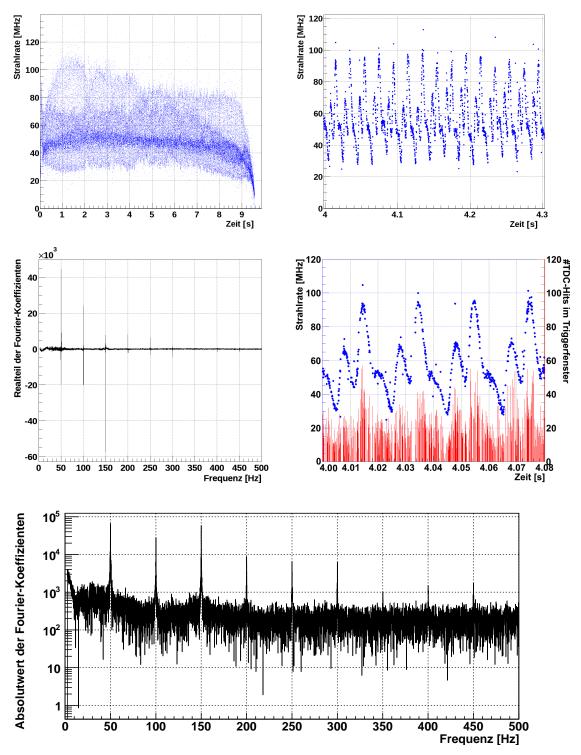

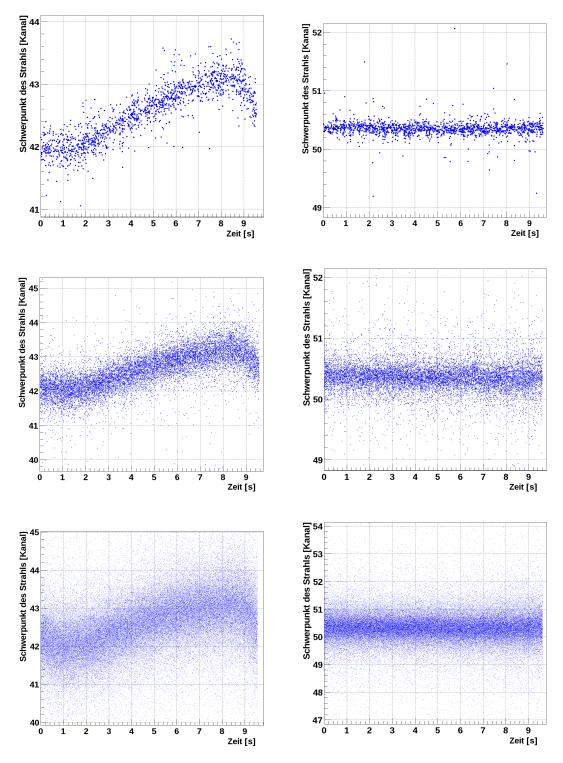

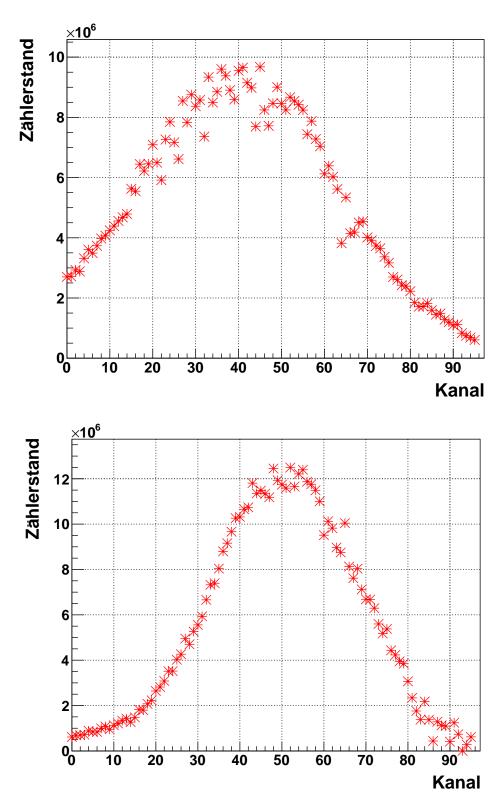

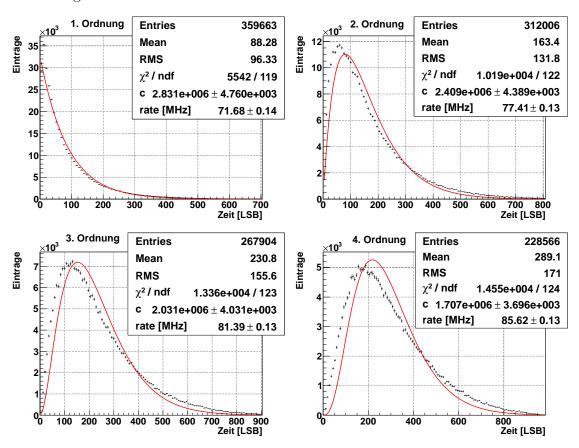

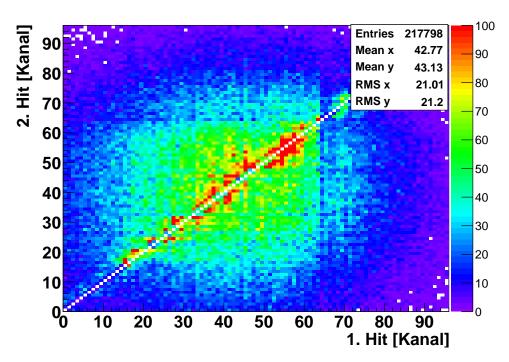

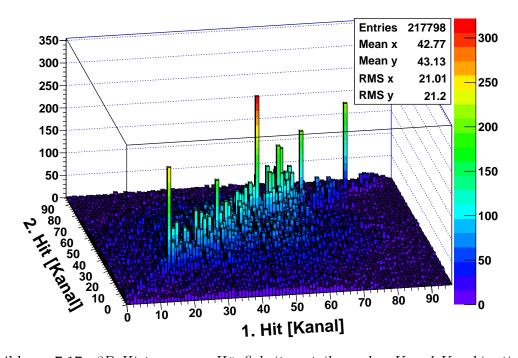

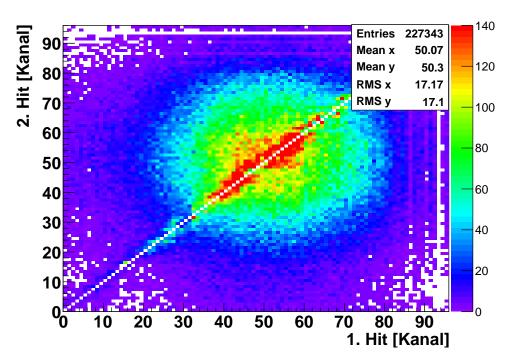

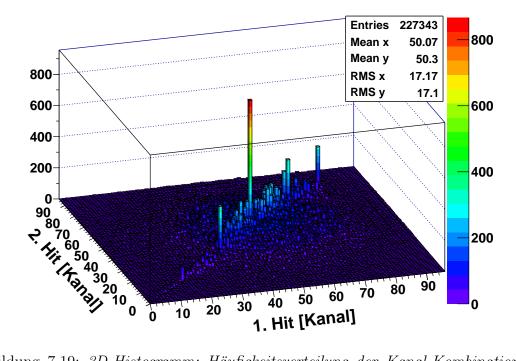

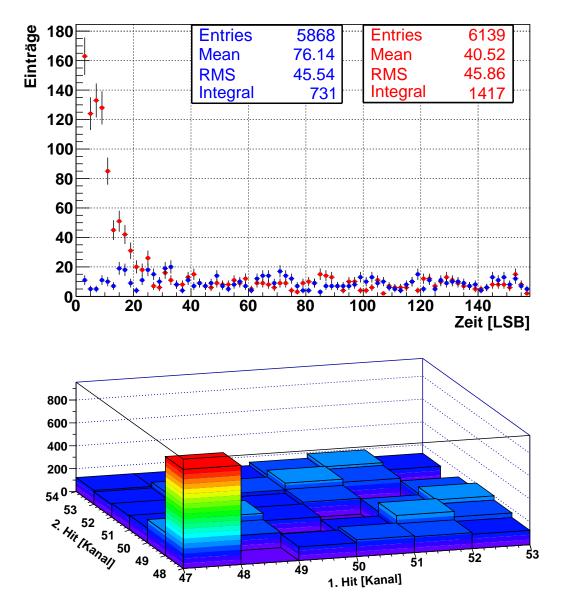

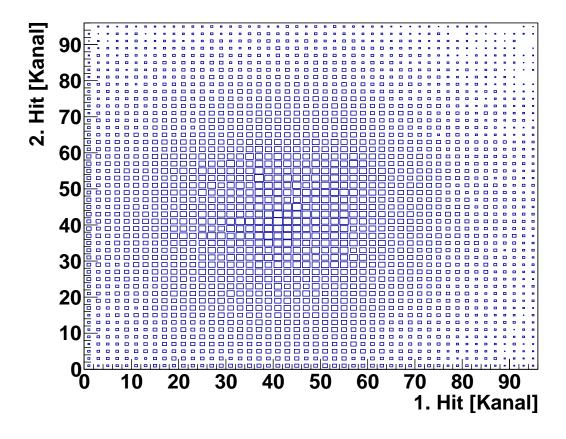

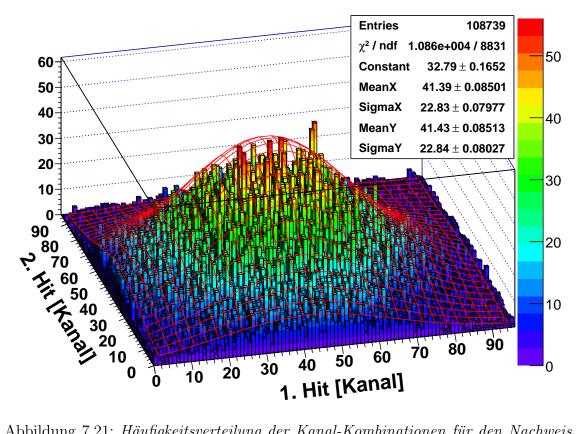

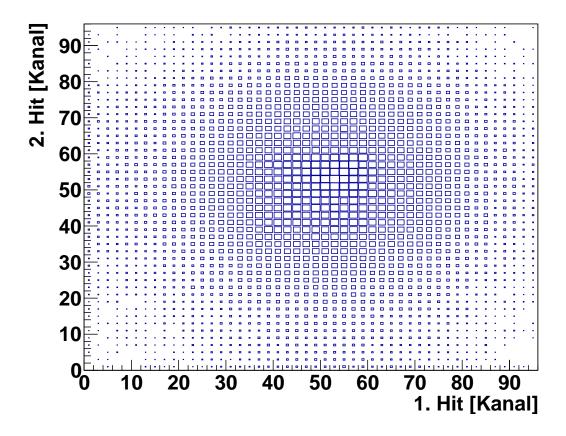

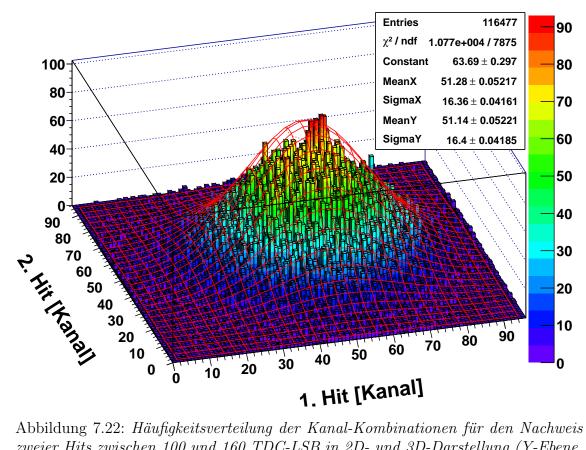

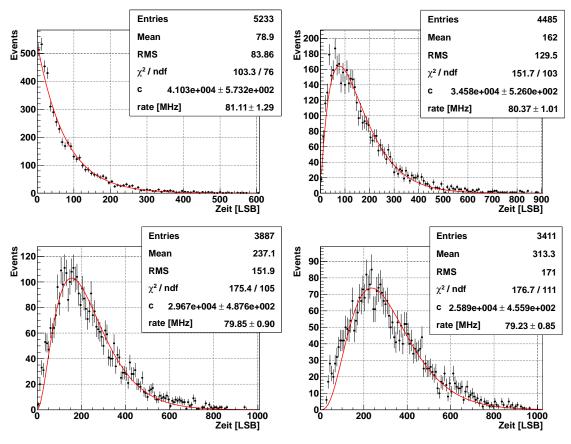

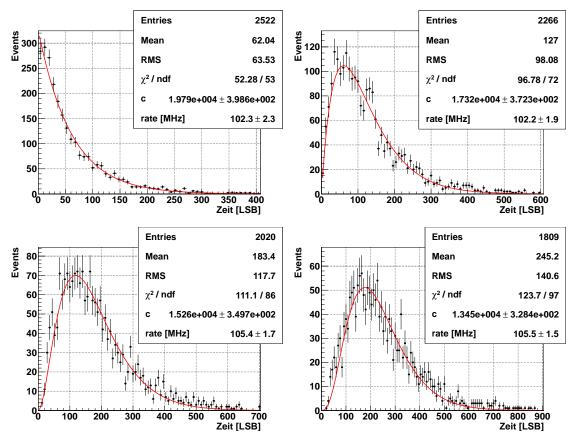

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|