# Development of new data acquisition system for COMPASS experiment

M. Bodlak, V. Frolov, V. Jary, S. Huber, I. Konorov, D. Levit, J. Novy, R. Salac and M. Virius

> Faculty of Nuclear Sciences and Physical Engineering Czech Technical University in Prague **CFRN**

COMPASS experiment

Introduction

### COMPASS experiment

- fixed target experiment at SPS accelerator at CERN

- study of hadron structure and hadron spectroscopy with high intensity muon and hadron beams

- data-taking started in 2002

- trigger rate up to 30 kHz, average event size up to 50 kB

- ▶ in spill data rate 1.5 GB/s and sustained data rate 500 MB/s

COMPASS experiment

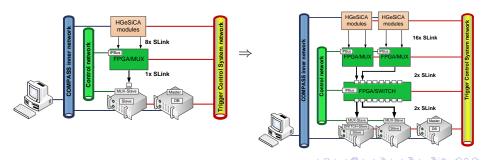

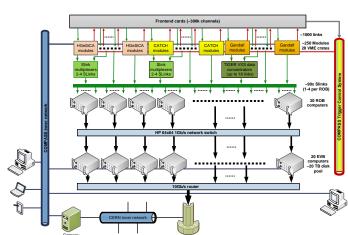

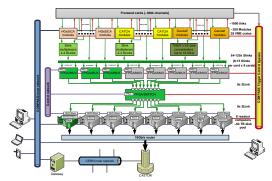

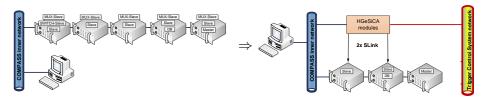

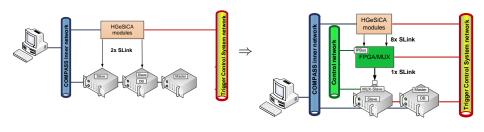

### Hardware/Software structure of the old DAQ

#### Network based E.B.

- ► \sim 1000 links to \sim 250 modules

- ➤ 90 S-links to 30 ROBs

- 50 online computers = 30 ROB+ 20 EB

- DAQ built in 2000

- sustained rate only of 500 MB/s

- Software event building

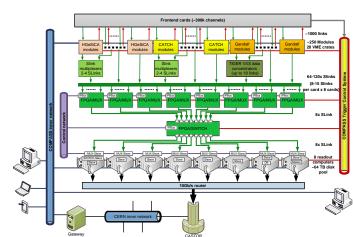

Hardware/Software design of the new DAQ

### Hardware/Software structure of the new DAQ

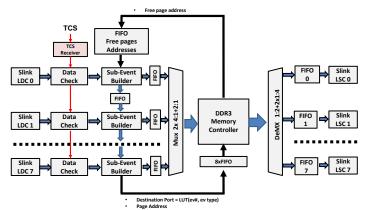

#### Hardware based E.B.

- 8 new DAQ modules as multiplexer

- 1 new DAQ modules as switch

- 8 readout computers

- 64 TB disk pool using RAID 10

- less components

- full events received by servers

- consistency check at many layer

### Hardware based event building

### HW event building in history

- CDF Fermilab [11]

- NA48 CERN [12],[13]

#### HW event building now with new FPGAs

- faster high speed serial links

- more flexible

- cheaper and more reliable

#### FPGA/SWITCH

Hardware/Software design of the new DAQ

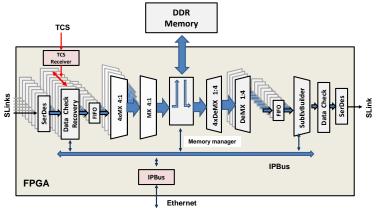

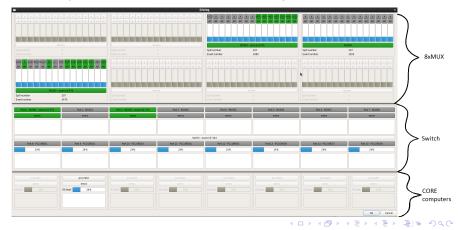

### DAQ unit

- TCS (Trigger Control System) receiver synchronization information

- 1 Gb Ethernet control system link (IPbus)

- 16xSerial links data links

- Slink (2 Gbps)

- Aurora (6.25 Gbps)

- 6 U VME form factor module → New DAQ fits in one 6 U VME crate

- AMC module, ATCA standard

- VIRTEX6 XC6VLX130T FPGA middle sized FPGA and relatively cheap (500 Euro/chip)

- 4 GB DDR3

- Module programmed as MX 15:1 or SW 8x8 (can be recompiled to any NxM configuration)

Hardware/Software design of the new DAQ

# New hardware parts

- 10 AMC cards + adapter cards

- 12 PCIe cards + 14 TCS receivers

- 6 TCS encoders/controllers

- Substitute obsolete and not available TTC encoders

- Wave length adapter from 1300 nm to 830 nm

- IPbus for control and monitoring, VME is only for power and cooling

### MX firmware

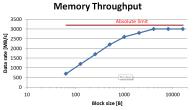

- buffering enough memory to store one spill

- sub-event building

### SW firmware

- DDR memory divided to 8k pages of 500kB each (bigger than maximum event size)

- Memory address is attached to data block header

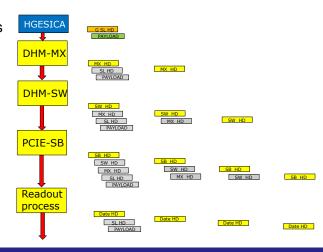

# Example of Data Flow and Data encapsulation

- Each step controls data and adds new header

- Data with errors thrown away and header generated

## Used software technologies

- ► C++, Python

- Ot framework

- DIM (Distributed Information Management System)

- IPbus suite for communication with FPGAs

- MySQL

- PHP, javascript

- Zabbix package used for computer resources monitoring

Present status - sub-DAQ tests

### Present status

- preparation for commissioning

- fraction of detectors connected

- testing of links, data transmission and data handling

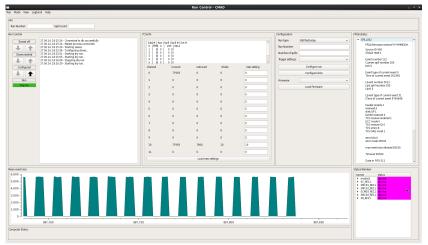

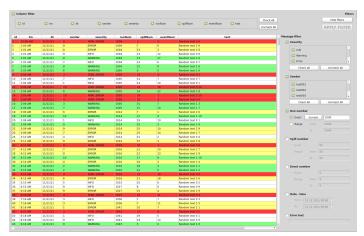

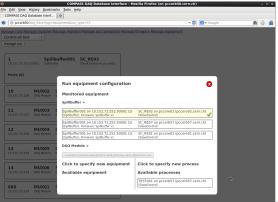

### Run control GUI

### DAQ system main window

component status overview and configuration

# MessageBrowser

Introduction

# Configuration interface

new configuration interface -> system fully configurable through web interface

- XML description of DAQ structure and FPGA registers automatically generated from DB

- used for IPbus communication, event consistency checks, parsing of information from registers

```

1 <?xml version="1.0" encoding="UTF-8"?>

2 <structure>

<hardware>

<type>Spillbuffer</type>

<action>remove</action>

<source>1</source>

<hardware>

<tvpe>MUX</tvpe>

<action>remove</action>

<source>560</source>

</hardware>

</hardware>

<hardware>

<type>Spillbuffer</type>

<action>renove</action>

16

<source>2</source>

</hardware>

<hardware>

<type>Spillbuffer</type>

20

<action>renove</action>

<source>3</source>

</hardware>

23 </structure>

```

```

<?xnl version="1.0" encoding="UTF-8"?>

<card id="REGISTERS">

<blook id="GB">

<register id="IDReg" address="0x0" permission="r">

<register_part id="FPGAFV" mask="0xffff" description="FPGA firmware version"/>

<register_part_id="DeID" mask="0xffff0000" description="Device ID"/>

<register id="SourceID" address="0x1" permission="rw">

<register_part_id="SID" mask="0x3ff" description="Source ID"/>

</register>

<register id="CurEvNun" address="0x2" permission="r">

<register_part_id="EN" mask="0xffffff" description="Event_number"/>

<register_part id="CSP" mask="0x7ff00000" description="Current spill number"/>

<register_part id="bx0" mask="0x80000000" description="bx0"/>

<register id="CurEvTT" address="0x3" permission="r">

<register_part id="ETOCE" mask="0x1f" description="Event type of current event"/>

<register_part id="TOCE" mask="0xffffffe0" description="Time of current event"/>

<register id="LSpEvNun" address="0x4" permission="r">

<register_part id="LEN" mask="0xfffff" description="LEvent number"/>

<register_part id="LSN" mask="0x7ff00000" description="Last spill number"/>

<register_part id="Lbx0" mask="0x80000000" description="Lbx0"/>

<register id="LSpEvTT" address="0x5" permission="r">

<register_part id="LETOCE" mask="0x1f" description="LEvent type of current event"/>

<register_part id="LTOCE" mask="0xffffffe0" description="LTime of current event"/>

<register id="TCSStat" address="0x6" permission="rw">

<register_part id="IPBUST" mask="0x1" description="IPBUS TCS reciever enable"/>

<register_part id="S1A2E" mask="0x6" description="Slink 1 and 2 enable"/>

<register_part id="bx000R" mask="0x38" description="bx000 reserved"/>

<register part id="TCSRE" mask="0x40" description="TCS receiver enabled"/>

<register_part id="ECCN" mask="0x80" description="ECC mode"/>

<register_part id="TCSRID" mask="0xff00" description="TCS receiver ID"/>

<register_part id="TCSE" mask="0xff0000" description="TCS errors"/>

<register part id="TCSDM" mask="0xff000000" description="TCS DAO mask"/>

<register id="FIFO1FL" address="0x7" permission="r">

<register part id="FN1" mask="0xefffffff" description="Filled memory 1"/>

<register id="FIFO2FL" address="0x8" permission="r">

<register part id="FN2" mask="0xefffffff" description="Filled memory 2"/>

```

## Setting up new DAQ

## Advantages of new DAQ

- More compact

- Flexible configuration

- Data verification on every step

- Less power demanding

- Easier to control (more time for reaction)

Summary

### Conclusion

- communication system tested

- sub-DAQ tested without detectors

- expected peak performance 1.5 GB/s and sustainable 1.2 GB/s but real performance still to be measured

- on the route to commissioning by end of July

#### References

M. Bodlak, et al. *Developing Control and Monitoring Software for the Data Acquisition System of the COMPASS Experiment at CERN*. Acta polytechnica: Scientific Journal of the Czech Technical University in Prague, Prague, CTU, 2013, issue 4. Available at: http://ctn.cvut.cz/ap/

M. Bodlak, et al. New data acquisition system for the COMPASS experiment. Journal of Instrumentation. 2013-02-01, vol. 8, issue 02, C02009-C02009. DOI: 10.1088/1748-0221/8/02/C02009. Available at: http://stacks.iop.org/1748-0221/8/i=02/a=C02009?key=crossref.a76044facdf29d0fb21f9eefe3305aa5

P. Abbon, et al.(the COMPASS collaboration): *The COMPASS experiment at CERN*. In: Nucl. Instrum. Methods Phys. Res., A 577, 3 (2007) pp. 455–518

T. Anticic, et al. (the ALICE collaboration): ALICE DAQ and ECS User's Guide. CERN, ALICE internal note, ALICE-INT-2005-015, 2005.

M. Bodlak, V. Jary, J. Novy: Software for the new COMPASS data acquisition system. In: COMPASS collaboration meeting, Geneva, Switzerland, 18 November 2011

L. Schmitt, et al.: The DAQ of the COMPASS experiment. In: 13th IEEE-NPSS Real Time Conference 2003, Montreal, Canada, 18–23 May 2003, pp. 439–444

V. Jary: Analysis and proposal of the new architecture of the selected parts of the software support of the COMPASS experiment Prague, 2012, Doctoral thesis, Czech Technical University in Prague

M. Bodlak: COMPASS DAQ Database Architecture and Support Utilities Prague, 2012, Master thesis, Czech Technical University in Prague

#### References

J. Novy: COMPASS DAQ - Basic Control System Prague, 2012, Master thesis, Czech Technical University in Prague

T. Anticic, et al. (ALICE DAQ Project): ALICE DAQ and ECS User's Guide CERN, EDMS 616039, January 2006.

T. M. Shaw, et al.: Architecture and development of the CDF hardware event builder IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 36, NO. 1, AUGUST 1989

E. Bal, et al.: The NA48' Data Acquisition System IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 45, NO. 4, AUGUST 1998

M. Wittgen, et al.: The NA48' Event-Building PC Farm IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 47, NO. 2, APRII. 2000

stable state, states that do nothing just wait for next command transfers states(not stable), do not accept commi

working states, stable untile command come or end condition is reached

| number | name               |

|--------|--------------------|

| 0      | Turned off         |

| 1      | Waiting            |

| 2      | Ready              |

| 3      | Configured         |

| 11     | Dry Run            |

| 12     | Run                |

| 21     | Starting           |

| 22     | Closing            |

| 23     | Starting slaves    |

| 24     | Turning off slaves |

| 25     | Configuring        |

| 26     | Unconfiguring      |

| 27     | Starting run       |

| 28     | Stoping Run        |

| 41-48  | Error 1-8          |

| stable state, states that do nothing just wait for next command |

|-----------------------------------------------------------------|

| transfere states(not stable), do not accept commands            |

| working states | atable untile com | mand some or on | d condition is re | oobo |

|----------------|-------------------|-----------------|-------------------|------|

| _      |               |

|--------|---------------|

| number | name          |

| 0      | Turned off    |

| 2      | Ready         |

| 3      | Configured    |

| 11     | Dry Run       |

| 12     | Run           |

| 21     | Starting      |

| 22     | Closing       |

| 25     | Configuring   |

| 26     | Unconfiguring |

| 27     | Starting run  |

| 28     | Stoping Run   |

| 41-48  | Error 1-8     |

error state

- System tests phase 1 communication tests [2]

- System tests phase 2 readout tests [2]

- System tests phase 3 multiplexer tests

- System tests phase 4 sub-DAQ tests

0000

- System tests phase 1 communication tests [2]

- System tests phase 2 readout tests [2]

- System tests phase 3 multiplexer tests

- System tests phase 4 sub-DAQ tests

0000

- System tests phase 1 communication tests [2]

- System tests phase 2 readout tests [2]

- System tests phase 3 multiplexer tests

- System tests phase 4 sub-DAQ tests

Route to final setup

- System tests phase 1 communication tests [2]

- System tests phase 2 readout tests [2]

- System tests phase 3 multiplexer tests

- System tests phase 4 sub-DAQ tests